filmov

tv

Master AXI protocol: AXI WRITE 1 Byte length

Показать описание

Are you eager to take your AXI protocol debugging skills to the next level?

The scientific method of one variable at a time (OVAT) is the key to success! We have perfected OVAT experiments and we're thrilled to share our expertise with you.

By keeping the length constant, you can observe the impact of AWADDR on WSTRB, and gain a deeper understanding of how these two parameters interact during the execution of an AXI transaction.

Learn/Test your AXI understanding further:

The scientific method of one variable at a time (OVAT) is the key to success! We have perfected OVAT experiments and we're thrilled to share our expertise with you.

By keeping the length constant, you can observe the impact of AWADDR on WSTRB, and gain a deeper understanding of how these two parameters interact during the execution of an AXI transaction.

Learn/Test your AXI understanding further:

Master AXI protocol: AXI WRITE 2 Byte length (4KB crossing)

Master AXI protocol: AXI WRITE 1 Byte length

AXI Introduction Part 1: How AXI works and AXI-Lite transaction example

The AXI Protocol

Master AXI protocol: AXI WRITE with FIXED ADDR and varying LENGTH

The AXI Protocol, AXI MM and AXI Streaming Interfaces [English]

The AXI Protocol in a multi-master system design

What is AXI (Part 1)

AXI Stream basics for beginners! A Stream FIFO example in Verilog.

What is AXI: Write Burst Example (Part 5)

AXI PROTOCOL - 1

What is AXI: Read Burst Example (Part 3)

What is AXI: Write Bursts (Part 4)

What is AXI Lite?

Lec87 - AXI bus handshaking

Transaction ordering in axi protocol || Amba Axi protocol ||

AXI/AHB Burst Beat Byte

AXI PROTOCOL - 2

Arm training – Introduction to the AMBA AXI protocol

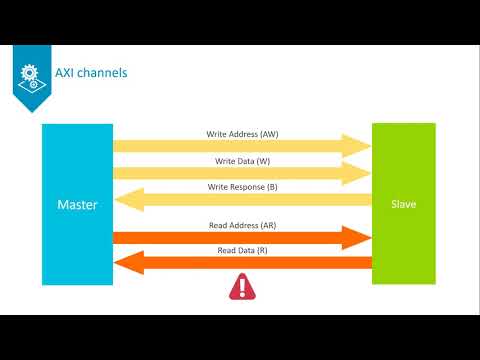

AXI Channels

How the AXI-style ready/valid handshake works

AXI’s Main features

AXI SES1 14JUN2023.mp4

Introduction to Axi Architecture || Amba Axi Bus protocol

Комментарии

0:11:51

0:11:51

0:05:45

0:05:45

0:17:40

0:17:40

0:00:47

0:00:47

0:10:38

0:10:38

0:18:56

0:18:56

0:01:38

0:01:38

0:07:04

0:07:04

0:12:11

0:12:11

0:05:41

0:05:41

2:14:37

2:14:37

0:07:48

0:07:48

0:04:35

0:04:35

0:09:50

0:09:50

0:21:12

0:21:12

0:12:22

0:12:22

0:24:41

0:24:41

1:55:13

1:55:13

0:03:05

0:03:05

0:02:14

0:02:14

0:15:11

0:15:11

0:02:13

0:02:13

1:49:59

1:49:59

0:13:21

0:13:21