filmov

tv

VHDL vs. Verilog - Which Language Is Better for FPGA

Показать описание

Finally an answer to the age-old question! VHDL vs. Verilog for FPGA. Who will be the champion in the most heated battle between the Hardware Description Languages. Find out now.

Like my content? Help me make more at Patreon!

VHDL vs. Verilog - Which Language Is Better for FPGA

Lec-3 | VHDL vs. Verilog - Which Language Is Better for FPGA | Verilog tutorials

Should I Learn Verilog or VHDL?

What language should I learn, Verilog or VHDL ??

Difference Between Verilog and VHDL

CPU vs FPGA

Verilog vs VHDL Side by Side HDL Comparison

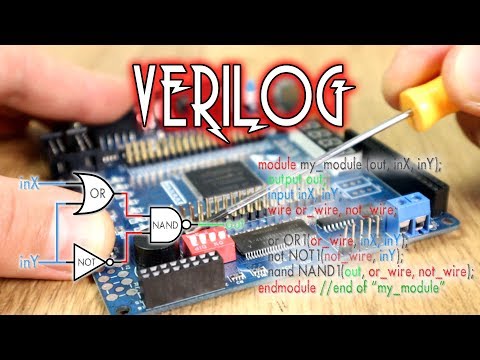

The best way to start learning Verilog

Alternatives to Verilog & VHDL: Bluespec & Chisel (exploring Hardware Description Languages)

The 'Do Anything' Chip: FPGA

Example Interview Questions for a job in FPGA, VHDL, Verilog

What's an FPGA?

003 16 bit vs ulogic vs std logic in vhdl verilog fpga

Comparision of VHDL & Verilog

FPGA with VHDL VS Verilog Module

Comparativo - VHDL vs. Verilog

Introduction to FPGA Part 1 - What is an FPGA? | Digi-Key Electronics

Generating Verilog or VHDL From a Schematic

Verilog intro - Road to FPGAs #102

VHDPlus IDE for Pros and University with VHDL or Verilog

Difference between VHDL and Verilog HDL

Verilog or VHDL for getting into VLSI Companies (India) | Rajveer Singh

VHDL versus SystemVerilog

Why Verilog is favourite HDL of VLSI Engineers || VHDL or Verilog || Hardware Description language

Комментарии

0:06:19

0:06:19

0:04:12

0:04:12

0:02:34

0:02:34

0:06:11

0:06:11

0:04:43

0:04:43

0:00:24

0:00:24

0:23:07

0:23:07

0:14:50

0:14:50

0:02:47

0:02:47

0:15:28

0:15:28

0:20:34

0:20:34

0:01:26

0:01:26

0:05:32

0:05:32

0:06:23

0:06:23

0:06:14

0:06:14

0:20:20

0:20:20

0:15:21

0:15:21

0:02:42

0:02:42

0:12:08

0:12:08

0:09:42

0:09:42

0:13:01

0:13:01

0:00:29

0:00:29

0:10:29

0:10:29

0:02:51

0:02:51