filmov

tv

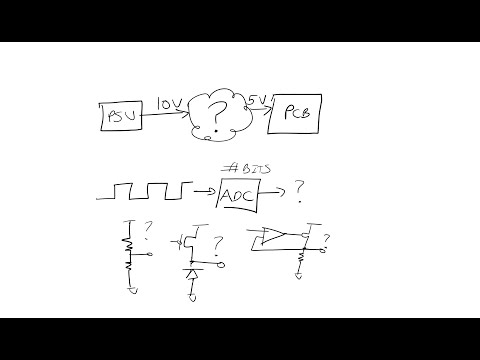

HWN - Analog Design Interview Question

Показать описание

Hi fellow (and future) engineers!

Have you ever wondered how you should prepare on your days prior to your interview? Don't take it from us, take it from a fellow ninja who just got his offer letter from Intel!

Welcome back to another episode of Hardware Ninja! Ever wondered how to get a job as a Hardware Designer in some of the top tech companies like Microsoft, Google, Tesla, Apple, Facebook, etc?

The interview process employs many application based questions whether you're a recent college grad or an experienced applicant. It doesn't matter if you want to work for Elon Musk, Tim Cook, or the up and coming start-up you heard about. We're here with curated material of real life technical interview questions.

Please consider subscribing to the channel and supporting our movement. Prospective job seekers (including yourself some day) will benefit from this resource.

#analogelectronics

#cmos

#vlsi

#vlsidesign

#designengineer

Background Music Merry Bay - Ghostrifter Official

Have you ever wondered how you should prepare on your days prior to your interview? Don't take it from us, take it from a fellow ninja who just got his offer letter from Intel!

Welcome back to another episode of Hardware Ninja! Ever wondered how to get a job as a Hardware Designer in some of the top tech companies like Microsoft, Google, Tesla, Apple, Facebook, etc?

The interview process employs many application based questions whether you're a recent college grad or an experienced applicant. It doesn't matter if you want to work for Elon Musk, Tim Cook, or the up and coming start-up you heard about. We're here with curated material of real life technical interview questions.

Please consider subscribing to the channel and supporting our movement. Prospective job seekers (including yourself some day) will benefit from this resource.

#analogelectronics

#cmos

#vlsi

#vlsidesign

#designengineer

Background Music Merry Bay - Ghostrifter Official

HWN - Analog Design Interview Question

HWN - Real 'Analog Design Engineer' Interview Questions

HWN - Digital/Analog Design Interview Question

HWN - '20-year Analog IC Designer' vs Our Team (Interview Question)

HWN - Analog Interview + Dojo Challenge

HWN - You're guaranteed to be asked this question on your interviews - 'Back to Basics&apo...

HWN - 'Hardware Engineer' Interview Question

HWN - Want to interview for NXP Semi? Study this!

Find gain by inspection : Analog Circuit design Interview questions

HWN - MOS Switches Interview Questions

HWN - Hardware Design Interview: HPF

What do they ask in Analog design interviews

'Analog Design Interview in VLSI Industry: Boost Your Job Pre ! 🕵️♀️✨ #AnalogDesignPrep #VLSI...

HWN - Real 'Hardware Engineer I' Interview Questions

HWN - Advanced Analog IC Design: Lecture 1

HWN - 'SoC Design Engineer' Interview Question (Offsets)

HWN - Real 'Digital Design Engineer' Interview Question

Cascade Current Mirror - Analog Circuit Design Interview

Interview Preparation for freshers : Analog Circuit Design

HWN - Apple Hardware Interview Question!

A Day in the life of an Analog IC Engineer

#vlsi interview questions #cmos #digitalelectronics #verilog #systemverilog #vlsiprojectcenters

HWN - Hardware Interviews Intro

Analog Devices Basic Interview Question

Комментарии

0:09:30

0:09:30

0:07:04

0:07:04

0:06:38

0:06:38

0:09:58

0:09:58

0:08:50

0:08:50

0:05:27

0:05:27

0:08:21

0:08:21

0:06:38

0:06:38

0:08:05

0:08:05

0:03:35

0:03:35

0:07:24

0:07:24

0:02:20

0:02:20

0:00:16

0:00:16

0:04:50

0:04:50

0:38:22

0:38:22

0:05:27

0:05:27

0:08:16

0:08:16

0:08:39

0:08:39

0:38:29

0:38:29

0:07:26

0:07:26

0:01:22

0:01:22

0:00:16

0:00:16

0:02:18

0:02:18

0:15:52

0:15:52