filmov

tv

Gate level simulation - Types of Gatelevel simulation

Показать описание

Rising complexity, tightening schedules and ever demanding time to market pressure are pushing the industry to move to the next level of abstraction for design representation . Even after efficiently using RTL simulations for a couple of decades, the industry is still relying on GLS (Gate level simulation) before sign off. Advancements in static verification tools like STA (static timing analysis) and Equivalence Checking (EC) have leveraged GLS to some extent but so far none of the tools have been able to abandon it. GLS still claims a significant portion of the verification cycle footprint.

The course is an attempt to help students / professionals to quickly ramp up on GLS basics and help to understand the GLS concepts .

The course is divided into 5 lectures .

Introduction - Introduction to course objectives and course requirements .

What is GLS - Introduction to GLS flow and challenges in running a GLS simulation .

Why GLS - Reasons for running a GLS simulation

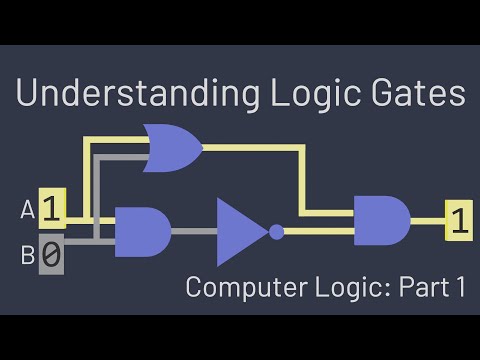

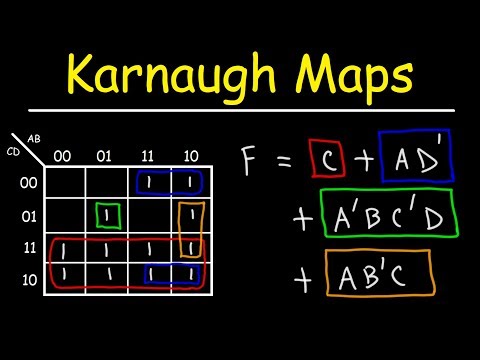

Types of GLS simulation - introduction to zero delay , unit delay , SDF simulation .

Bugs found in GLS simulation - common bug types found only in GLS simulation.

Click on the links below to access different VLSI topics on interview questions . Please help to like ,share and subscribe to reach a wider audience .

Digital RTL design and verilog interview questions

Physical design interview questions

Static timing analysis interview questions

Clock domain crossing and synchronizers interview questions

System verilog UVM step by step guide

System verilog UVM interview questions

AHB and APB interview questions

SPI protocol and interview questions

I2c interview questions

The course is an attempt to help students / professionals to quickly ramp up on GLS basics and help to understand the GLS concepts .

The course is divided into 5 lectures .

Introduction - Introduction to course objectives and course requirements .

What is GLS - Introduction to GLS flow and challenges in running a GLS simulation .

Why GLS - Reasons for running a GLS simulation

Types of GLS simulation - introduction to zero delay , unit delay , SDF simulation .

Bugs found in GLS simulation - common bug types found only in GLS simulation.

Click on the links below to access different VLSI topics on interview questions . Please help to like ,share and subscribe to reach a wider audience .

Digital RTL design and verilog interview questions

Physical design interview questions

Static timing analysis interview questions

Clock domain crossing and synchronizers interview questions

System verilog UVM step by step guide

System verilog UVM interview questions

AHB and APB interview questions

SPI protocol and interview questions

I2c interview questions

0:02:44

0:02:44

0:03:32

0:03:32

0:03:27

0:03:27

0:44:48

0:44:48

0:03:20

0:03:20

0:06:38

0:06:38

0:07:28

0:07:28

0:00:06

0:00:06

0:07:19

0:07:19

0:09:33

0:09:33

0:12:16

0:12:16

0:07:26

0:07:26

0:50:01

0:50:01

0:46:37

0:46:37

0:16:45

0:16:45

0:00:14

0:00:14

0:00:16

0:00:16

0:45:00

0:45:00

0:14:50

0:14:50

0:00:18

0:00:18

0:09:03

0:09:03

0:00:29

0:00:29

0:29:44

0:29:44

0:11:12

0:11:12