filmov

tv

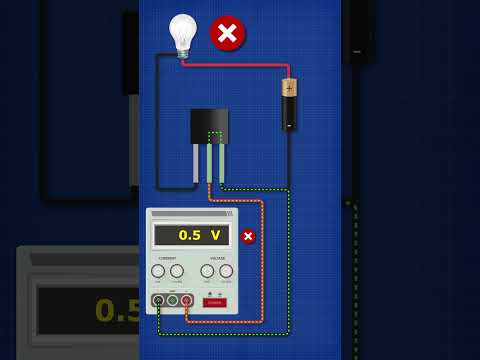

Working of JFET (Negative Voltage at the Gate)

Показать описание

Analog Electronics: Working of JFET (Negative Voltage at the Gate)

Topics Covered:

1. Working of junction field effect transistor.

2. Working of JFET when the voltage between gate and source is negative (or less than zero) and the voltage between drain and source is greater than zero.

3. Effect on depletion region.

Topics Covered:

1. Working of junction field effect transistor.

2. Working of JFET when the voltage between gate and source is negative (or less than zero) and the voltage between drain and source is greater than zero.

3. Effect on depletion region.

Working of JFET (Negative Voltage at the Gate)

Working of JFET for negative Gate voltage

Working of JFET (Negative Voltage at the Gate)

JFET: Construction and Working Explained

Lecture 5-working of JFET (NEGATIVE VOLTAGE AT GATE)

Working of JFET (Zero Voltage at the Gate)

The VI Characteristics and Operating Regions of a JFET

What is a JFET and how does it work?

Working of JFET ( Negative voltage at a Gate terminal)

Working of FET with negative gate to source voltage in Tamil I Electron devices in Tamil

Semiconductor Devices: JFET Voltage Controlled Resistor

Output or Drain Characteristics of JFET

Construction and Working of JFET

Exploring How JFETs (Junction Field-Effect Transistors) Work! - DC to Daylight

JFET - Construction & Working - Easy Explanation - Electronics

Characteristics of JFET - Field Effect Transistor - Basic Electronics

6 Ways: How to Convert a Positive Input Voltage into a Negative Output Voltage

🔴 JFET (PART 2) - Negative voltage in GATE || for B.Sc. in HINDI

Effect of Depletion Region, Output or Drain Characteristics, Transfer Characteristics of JFET

jfet construction and working (for negative gate source voltage)

Transistors Explained - What is a transistor?

Why do Junction Transistors Amplify Current and not Voltage

PN Junction Hiding in a JFET

JFET (Junction Field Effect Transistor) Working & Characteristics (Basic Electronics)

Комментарии

0:08:23

0:08:23

0:07:45

0:07:45

0:03:37

0:03:37

0:16:19

0:16:19

0:09:17

0:09:17

0:11:03

0:11:03

0:05:16

0:05:16

0:06:29

0:06:29

0:15:25

0:15:25

0:08:49

0:08:49

0:11:25

0:11:25

0:14:59

0:14:59

0:09:06

0:09:06

0:15:38

0:15:38

0:04:16

0:04:16

0:07:31

0:07:31

0:08:58

0:08:58

0:18:13

0:18:13

0:17:15

0:17:15

0:13:27

0:13:27

0:01:00

0:01:00

0:12:43

0:12:43

0:00:55

0:00:55

0:18:20

0:18:20