filmov

tv

Stitching Via Deep Dive | PCB Layout

Показать описание

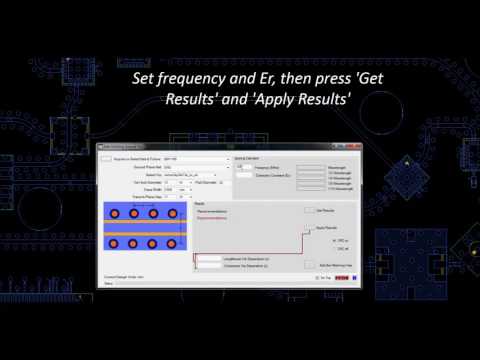

Tech Consultant Zach Peterson jumps into a stitching vias exploration in this video. He focuses specifically on their uses, as well as how to both size and space them correctly.

0:00 Intro

0:36 When to Use Stitching Vias

2:32 Tying Together Copper Pour

4:59 Grid Size?

6:57 Layer Transitions

10:31 Shielding

14:49 Checking the Buses

Don't forget to follow us on social to stay up-to-date on the latest Altium Academy content.

The Altium Academy is an online experience created to bring modern education to PCB Designers and Engineers all across the world. Here you can access a vast library of free training and educational content covering everything from basic design to advanced principles and step-by-step walkthroughs. Join industry legends as they share their career knowledge, review real-life design projects, or learn how to leverage one of Altium's leading design tools. No matter your level of experience, the Altium Academy can help you become a better Designer and Engineer!

About Altium LLC

Altium LLC (ASX:ALU), a global software company based in San Diego, California, is accelerating the pace of innovation through electronics. From individual inventors to multinational corporations, more PCB designers and engineers choose Altium software to design and realize electronics-based products.

#Altium #PCBdesign #ElectronicsDesign

0:00 Intro

0:36 When to Use Stitching Vias

2:32 Tying Together Copper Pour

4:59 Grid Size?

6:57 Layer Transitions

10:31 Shielding

14:49 Checking the Buses

Don't forget to follow us on social to stay up-to-date on the latest Altium Academy content.

The Altium Academy is an online experience created to bring modern education to PCB Designers and Engineers all across the world. Here you can access a vast library of free training and educational content covering everything from basic design to advanced principles and step-by-step walkthroughs. Join industry legends as they share their career knowledge, review real-life design projects, or learn how to leverage one of Altium's leading design tools. No matter your level of experience, the Altium Academy can help you become a better Designer and Engineer!

About Altium LLC

Altium LLC (ASX:ALU), a global software company based in San Diego, California, is accelerating the pace of innovation through electronics. From individual inventors to multinational corporations, more PCB designers and engineers choose Altium software to design and realize electronics-based products.

#Altium #PCBdesign #ElectronicsDesign

Комментарии

0:17:00

0:17:00

0:03:19

0:03:19

0:02:55

0:02:55

0:04:38

0:04:38

0:00:59

0:00:59

0:17:01

0:17:01

0:00:32

0:00:32

0:00:49

0:00:49

0:18:54

0:18:54

0:21:12

0:21:12

0:05:44

0:05:44

0:13:51

0:13:51

0:14:12

0:14:12

0:01:38

0:01:38

0:01:49

0:01:49

1:01:07

1:01:07

0:00:23

0:00:23

0:15:55

0:15:55

0:05:13

0:05:13

0:04:56

0:04:56

0:01:36

0:01:36

0:00:28

0:00:28

0:00:59

0:00:59

0:08:34

0:08:34