filmov

tv

What is Dual Edge Triggered Flip Flop? How to design it?🤔 Explained 👍

Показать описание

🙏 Hey guys , in this video I have explained about DETFF , leave a comment if you have any doubts, please subscribe it will help me alot 👍 thanks for watching 😊

What is Dual Edge Triggered Flip Flop? How to design it?🤔 Explained 👍

DUAL EDGE-TRIGGERED D-TYPE FLIP-FLOP WITH LOW POWER CONSUMPTION

DUAL EDGE-TRIGGERED D-TYPE FLIP-FLOP WITH LOW POWER CONSUMPTION

Design of a Dual Edge Flip Flop

14 differences between Dual Sense EDGE vs. Standard PS5 Controller

74HC109N Dual JK flip-flop with set and reset; positive-edge trigger

Using Edge Trigger

Timing Diagram for Dual Edge JK Flip Flop

Electronics: Dual edge triggered D flip flip CMOS implementation. Less than 20 transistor

HD74LS112 Dual J-K Negative-edge-triggered Flip-Flops (with Preset and Clear)

Working of Edge-Triggered D Flip Flop

D-type flip flop rising edge trigger explained | EDUQAS GCSE Electronics

Dual Sense Edge back button trick!! #ps5 #dualsenseedge #dualsense #fortnite #hogwartslegacy

7474 integrated circuit Dual positive edge triggered D flip flop preset clear complimentary outputs

Level Trigger vs Edge Trigger Flip Flop | Types of Triggering

LOW POWER REDUNDANT TRANSITION FREE TSPC DUAL EDGE TRIGGERING FLIP FLOP USING SINGLE TRANSISTOR CLOC

JK Flip Flop Timing Diagrams

D Flip-Flop Negative Edge Triggered Demonstration on a Breadboard.

D Flip-Flop Explained | Truth Table and Excitation Table of D Flip-Flop

What is a D Flip-Flop? | FPGA concepts

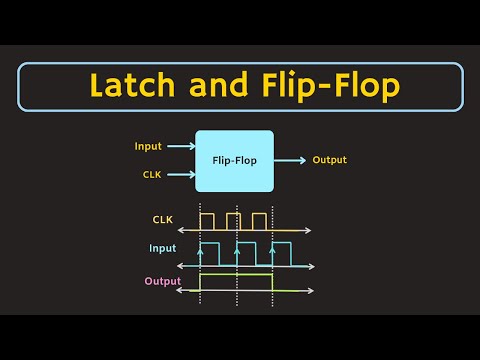

Latch and Flip-Flop Explained | Difference between the Latch and Flip-Flop

Dual edge register

74HC374N Octal D-type flip-flop; positive edge-trigger; 3-state

Dual J-K negative edge-triggered flip-flop with CLEAR || Aplication Relevant Data

Комментарии

0:07:21

0:07:21

0:00:59

0:00:59

0:00:52

0:00:52

0:04:18

0:04:18

0:05:56

0:05:56

0:00:21

0:00:21

0:01:41

0:01:41

0:05:35

0:05:35

0:02:47

0:02:47

0:00:29

0:00:29

0:12:25

0:12:25

0:12:30

0:12:30

0:00:39

0:00:39

0:10:59

0:10:59

0:08:24

0:08:24

0:02:40

0:02:40

0:06:33

0:06:33

0:00:11

0:00:11

0:11:53

0:11:53

0:08:59

0:08:59

0:09:50

0:09:50

0:12:55

0:12:55

0:00:26

0:00:26

0:03:21

0:03:21