filmov

tv

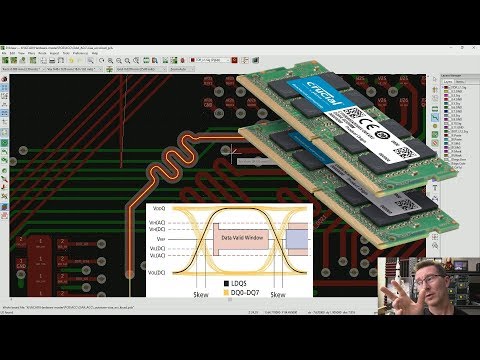

EEVblog #1247 - DDR Memory PCB Propagation Delay & Layout

Показать описание

When does PCB propagation delay matter in PCB layout?

Dave goes down the rabbit hole from DIY TTL processor design to DDR memory design and layout.

DDR memory termination.

What is a timing budget? When is it important?

How does signal integrity matter?

When do you have to do serpentine PCB traces to match trace and differential pair lengths?

Micron DDR memory timing budget design:

#PCB #Layout #DDRmemory

Bitcoin Donations: 38y7DE8HEHNj8fGDtUr4PkCn9nWxiorvvy

Litecoin: ML7oQokTwB38bgzzjLDbRV97HKAHuwRfHA

Ethereum: 0x11AceA38DCA9DbFfB4F35f3F746af65F9dED28ce

Support the EEVblog through Patreon!

Buy anything through that link and Dave gets a commission at no cost to you.

Stuff I recommend:

Donate With Bitcoin & Other Crypto Currencies!

Dave goes down the rabbit hole from DIY TTL processor design to DDR memory design and layout.

DDR memory termination.

What is a timing budget? When is it important?

How does signal integrity matter?

When do you have to do serpentine PCB traces to match trace and differential pair lengths?

Micron DDR memory timing budget design:

#PCB #Layout #DDRmemory

Bitcoin Donations: 38y7DE8HEHNj8fGDtUr4PkCn9nWxiorvvy

Litecoin: ML7oQokTwB38bgzzjLDbRV97HKAHuwRfHA

Ethereum: 0x11AceA38DCA9DbFfB4F35f3F746af65F9dED28ce

Support the EEVblog through Patreon!

Buy anything through that link and Dave gets a commission at no cost to you.

Stuff I recommend:

Donate With Bitcoin & Other Crypto Currencies!

EEVblog #1247 - DDR Memory PCB Propagation Delay & Layout

EEVblog #1242 - Memory LCD+Supercaps+Low Power Design

EEVblog #1245 - A Most Excellent REPAIR: IBM PCjr Keyboard

EEVblog #1251 - LifeSaber Kickstarter - A Master of None FAIL

eevBLAB #50 - Great Idea At The Wrong Time!

EEVblog #1246 - Dumpster TV to Retro RGB Monitor Conversion

EEVblog #1249 - TUTORIAL: Timing Diagrams Explained

EEVblog #1241 - Power Up Display Counter Project - Part 1

EEVblog #1262 - Designing a Flex PCB + uSupply Update

EEVblog #968 - Mystery EDA Package

EEVblog #1252 - LED Panel Lighting Flicker Investigated

IBM BGA Thermal Futility...

EEVblog #1015 - Beware Evil (But Clever) DC Jacks!

DDR4 timings explained 1: tCL tRCD tCR // Literally just a single read burst operation

EEVblog #1244 - Mailbag

eevBLAB #65 - No Professional Engineer Title For You!

EEVblog #1316 - Quantum Computing for Electrical Engineers

EEVblog #58 - Warm and Fuzzy FPGA Troubleshooting

EEVblog 1379 - What's all this NPLC Stuff Anyhow?

How to measure DDR4 memories

Tutorial Cadence Autointeractive Convert Corner

EEVBLOG/UEI 121GW Part 6, Destructive Testing and Final Thoughts.

EEVblog #1365 - Viewer PCB & Circuit Design Review

EEVblog #1196 - Custom Heat Sink Design (µSupply Part 19)

Комментарии

0:39:34

0:39:34

0:27:29

0:27:29

0:28:14

0:28:14

0:28:49

0:28:49

0:17:52

0:17:52

0:29:41

0:29:41

0:36:41

0:36:41

0:36:43

0:36:43

0:55:19

0:55:19

0:27:45

0:27:45

0:19:34

0:19:34

0:17:01

0:17:01

0:08:03

0:08:03

0:29:16

0:29:16

0:49:54

0:49:54

0:19:54

0:19:54

0:29:55

0:29:55

0:16:16

0:16:16

0:18:26

0:18:26

1:24:08

1:24:08

0:01:02

0:01:02

1:00:18

1:00:18

0:45:10

0:45:10

0:24:51

0:24:51