filmov

tv

Timing Constraints in Sequential Synchronous Circuits

Показать описание

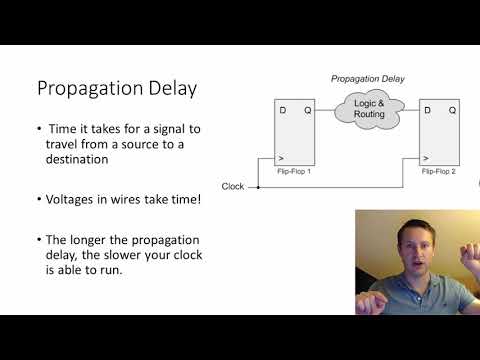

This is a tutorial on timing in sequential synchronous circuits composed of edge-triggered flip flops and combinational logic. In this video, I present some timing constraints and show how to ensure that they are satisfied.

Table of contents:

00:00 - Introduction

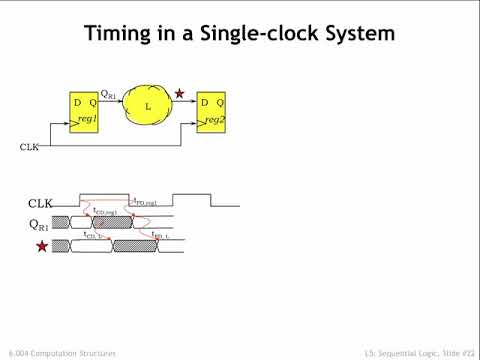

00:34 - Timing diagrams

03:11 - Flip flop timing

08:35 - Flip flop with feedback

15:48 - Linearization of flip flop paths

17:23 - Flip flop with more complicated feedback

18:52 - More complicated example

24:21 - Conclusion

Table of contents:

00:00 - Introduction

00:34 - Timing diagrams

03:11 - Flip flop timing

08:35 - Flip flop with feedback

15:48 - Linearization of flip flop paths

17:23 - Flip flop with more complicated feedback

18:52 - More complicated example

24:21 - Conclusion

Timing Constraints in Sequential Synchronous Circuits

62 - Sequential Circuits Timing Analysis

VLSI - Lecture 7e: Basic Timing Constraints

DVD - Lecture 5b: Timing Constraints

Advanced VLSI Design: Static Timing Analysis

Introduction to SDC Timing Constraints

Setup Time and Hold Time of Flip Flop Explained | Digital Electronics

5.2.5 Sequential Circuit Timing

Synthesis/STA SDC constraints - set_input_delay and set_output_delay constraints

VLSI - Lecture 7c: Timing Parameters

DDCA Ch3 - Part 13: Timing

Masterclass on Timing Constraints

Basic Static Timing Analysis: Setting Timing Constraints

Timing Diagram for a sequential circuit

DVD - Lecture 5: Timing (STA)

VLSI - Lecture 7b: Sequential Logic Elements

How to Apply Timing Constraints Using the Libero® Constraint Manager

Setup, Hold, Propagation Delay, Timing Errors, Metastability in FPGA

⨘ } VLSI } 6 } Synchronous Design, Flip-Flops, Clocks & Timing } LEPROF }

Synchronous sequential circuit design| Terminologies and timing parameters

Salsa Night in IIT Bombay #shorts #salsa #dance #iit #iitbombay #motivation #trending #viral #jee

Input delay constraints for interface setup/hold analysis

Understanding Timing Analysis in FPGAs

How to fix Timing Errors in your FPGA design during Place and Route, meeting clock constraints

Комментарии

0:24:55

0:24:55

0:26:48

0:26:48

0:25:55

0:25:55

0:14:39

0:14:39

0:26:17

0:26:17

0:20:21

0:20:21

0:17:37

0:17:37

0:06:52

0:06:52

0:13:33

0:13:33

0:22:57

0:22:57

0:25:17

0:25:17

0:57:12

0:57:12

0:50:45

0:50:45

0:12:39

0:12:39

2:01:33

2:01:33

0:24:16

0:24:16

0:06:23

0:06:23

0:11:08

0:11:08

0:18:05

0:18:05

0:42:08

0:42:08

0:00:14

0:00:14

0:08:43

0:08:43

0:29:41

0:29:41

0:14:00

0:14:00