filmov

tv

FPGA Design with MATLAB, Part 1: Why Use MATLAB and Simulink

Показать описание

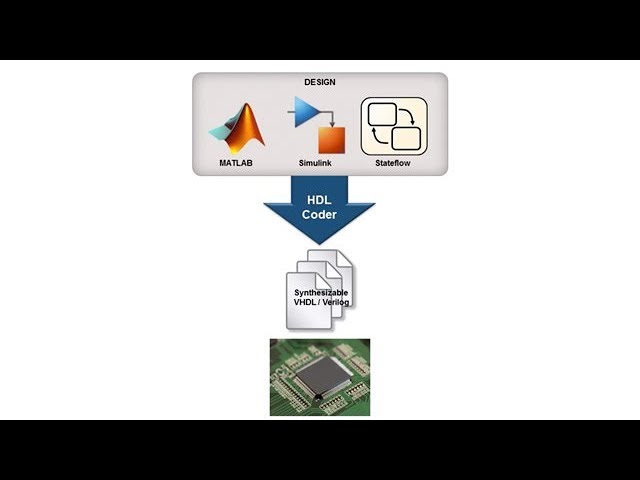

HDL Coder™ generates synthesizable VHDL® or Verilog® RTL from MATLAB® functions, Simulink® models, and Stateflow® charts that can be used to target FPGA or ASIC hardware. This tutorial uses a simple signal-processing algorithm to show the typical steps our customers follow to adapt their high-level algorithms with hardware architecture detail so they can be implemented efficiently in hardware and verified at each step.

This video covers:

- Key considerations for hardware design: streaming data and fixed resources

- Strengths of MATLAB and Simulink and how to leverage each for hardware design

- Overview of the workflow, including verification of each step

- HDL Coder Self-Guided Tutorial overview

- Introduction to the MATLAB golden reference algorithm

- Adapting the frame-based algorithm to a streaming algorithm

--------------------------------------------------------------------------------------------------------

© 2019 The MathWorks, Inc. MATLAB and Simulink are registered

trademarks of The MathWorks, Inc.

This video covers:

- Key considerations for hardware design: streaming data and fixed resources

- Strengths of MATLAB and Simulink and how to leverage each for hardware design

- Overview of the workflow, including verification of each step

- HDL Coder Self-Guided Tutorial overview

- Introduction to the MATLAB golden reference algorithm

- Adapting the frame-based algorithm to a streaming algorithm

--------------------------------------------------------------------------------------------------------

© 2019 The MathWorks, Inc. MATLAB and Simulink are registered

trademarks of The MathWorks, Inc.

FPGA Design with MATLAB, Part 1: Why Use MATLAB and Simulink

FPGA Design with MATLAB, Part 3: Architecting Efficient Hardware

FPGA Design with MATLAB, Part 2: Modeling Hardware in Simulink

FPGA Design with MATLAB, Part 4: Converting to Fixed Point

MATLAB to FPGA in 5 Steps

Set Up a FPGA Design Project | Getting Started with the Avnet ZUBoard, Part 1

FPGA Design with MATLAB, Part 5: Generating and Synthesizing RTL

FPGA, ASIC, and SoC Development with MATLAB and Simulink

FPGA Design with MATLAB/Simulink [System Generator]-Udemy Course

Prototype FPGA Design on Hardware from the MATLAB Command Line

Part 1_ Design & FPGA Implementation of Automatic Dependent Surveillance–Broadcast Using Matlab...

Program the Design onto an FPGA Using Vivado | Getting Started with the Avnet ZUBoard, Part 4:

Verifying an FPGA Implementation of an LTE Turbo Decoder - MATLAB and Simulink Tutorial

Generating FPGA Implementation Metrics for an LTE HDL Toolbox Block - MATLAB and Simulink Tutorial

Deep Learning on a Xilinx FPGA with MATLAB Code

HDL Coder Clock Rate Pipelining, Part 2: Optimization - MATLAB and Simulink Video

Part 2_ FPGA Implementation of Automatic Dependent Surveillance–Broadcast Using Matlab Simulink

Designing a Datapath from an FPGA to a Processor with SoC Blockset: Xilinx Deployment

FPGA in the Loop with PCI Express Altera Cyclone V GT

Vision Processing for FPGA, Part 4: Targeting a Lane Detection Design to a Xilinx Zynq Device

Vision Processing for FPGA Part 5 Hardware Software Prototyping of a Lane Detection Design

Designing a Datapath from an FPGA to a Processor with SoC Blockset: Modeling and Simulation

HDL Verifier: FPGA Data Capture

MATLAB Interfacing with an FPGA Board

Комментарии

0:04:20

0:04:20

0:04:49

0:04:49

0:04:43

0:04:43

0:05:42

0:05:42

0:23:04

0:23:04

0:03:53

0:03:53

0:05:24

0:05:24

0:37:37

0:37:37

0:03:59

0:03:59

0:05:31

0:05:31

0:11:21

0:11:21

0:03:57

0:03:57

0:03:52

0:03:52

0:05:14

0:05:14

0:03:26

0:03:26

0:05:42

0:05:42

0:13:26

0:13:26

0:05:44

0:05:44

0:02:53

0:02:53

0:04:59

0:04:59

0:05:04

0:05:04

0:06:12

0:06:12

0:04:10

0:04:10

0:05:07

0:05:07