filmov

tv

NOR CMOS | Digitaltechnik

Показать описание

Achtung Fehler im Video. Unsere pnp Transistoren sind nicht korrekt gezeichnet! Wir entschuldigen uns dafür.

Mehr Videos/More videos

CMOS Grundschaltungen:

Gatterschaltung zeichnen:

LOGIKGATTER/ Logic gate:

Falls ihr etwas nicht versteht, dann schreibt uns doch einfach eine Nachricht und wir machen ein Video drüber.

NOR CMOS | Digitaltechnik

CMOS GRUNDWISSEN / CMOS BASICS | Digitaltechnik

NAND CMOS | Digitaltechnik

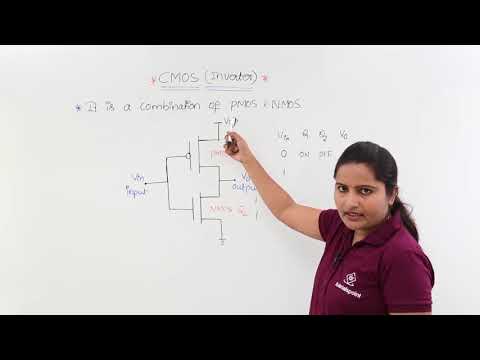

CMOS INVERTER | Digitaltechnik

CMOS Logik - REALISIERUNG der Grundschaltungen - NAND,NOR,NOT,AND,OR

What is a CMOS? [NMOS, PMOS]

CMOS NETZANALYSE (NETWORK ANALYSIS) | Digitaltechnik

CMOS Logic Gates Explained | Logic Gate Implementation using CMOS logic

Basic Introduction of the Current Mirrors using CMOS transistors

#01.5 CMOS Logikgatter ★ DIGITALTECHNIK

CMOS NOR Gate

CMOS NAND Gate

abc von TTL und CMOS Teil 1 - Logikgatter, Funktion und Beschaltung

3.3(e) - CMOS Gates (NOR)

NOR gate using CMOS technology #electronics #vlsiprojects #vlsi #tech #digital #diy

CMOS NAND gate #cmos #nandgate #digitalelectronics #logicgates

Understanding Logic Gates

Solved Problems on CMOS Logic Circuits | Digital Electronics

CMOS Circuits - Pull Down and Pull Up Network, PDN, PUN, Karnaugh Map, Digital Logic, NOT, NAND, XOR

CMOS Logic Gates

CMOS | Complement Metal Oxide Semiconductor | Digital Circuits | Logic Gates | Logic Family

What is CMOS Inverter || Simulation of CMOS Inverter

CMOS Not Gate #cmos #notgate #electricalcircuit #circuit #analogcircuit

CMOS Inverter

Комментарии

0:03:37

0:03:37

0:04:16

0:04:16

0:03:48

0:03:48

0:01:55

0:01:55

0:06:51

0:06:51

0:07:54

0:07:54

0:05:01

0:05:01

0:28:11

0:28:11

0:16:53

0:16:53

0:06:22

0:06:22

0:09:02

0:09:02

0:08:02

0:08:02

0:14:11

0:14:11

0:06:34

0:06:34

0:00:16

0:00:16

0:00:57

0:00:57

0:07:28

0:07:28

0:20:02

0:20:02

0:12:07

0:12:07

0:05:50

0:05:50

0:07:05

0:07:05

0:00:05

0:00:05

0:00:34

0:00:34

0:04:55

0:04:55