filmov

tv

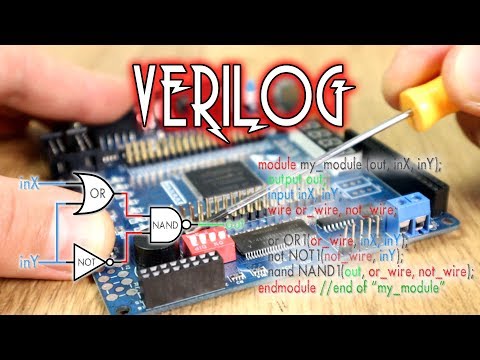

Introduction to Verilog HDL using Free Software Icarus, GTKWave, and VS Code

Показать описание

00:03 What is Hardware Description Language?

00:23 Advantage of Textual Form Design

01:03 Altera HDL or AHDL

01:19 Just-Another HDL (JHDL)

01:33 VHSIC HDL (VHDL)

01:56 Meaning of VHSIC

02:30 Verilog

02:13 SystemVerilog

02:36 Test Bench

02:59 Logic Synthesis

03:06 Netlist

03:13 Verilog Modeling Styles

03:19 Gate-level Modeling

03:26 DataFlow Modeling

03:36 Behavioural Modeling

03:53 Verilog is case-sensitive just like C

04:06 White spaces, tabs, new lines are ignored

04:13 Keywords are lowercase

04:26 How to name a variable

04:36 System tasks or function starts with dollar sign

04:43 One line and multi-line comments

05:06 note on the old and new version of the syntax

05:13 module endmodule keyword pair

05:29 module name

05:33 port list

05:59 input and output keywords

06:19 Statements are terminated by semicolon

06:33 Icarus is Free and can be used offline

06:49 How to install iverilog

07:33 How to install Icarus for Windows

10:03 Where the verilog bin libraries or executables?

10:23 How to update PATH environment variables

11:46 How to check if iverilog is installed

11:56 How to view iverilog version

12:23 How to install Visual Studio Code Text Editor

14:06 How to customize or configure VS Code for Verilog

14:19 Verilog HDL extension

15:46 What is the purpose of GTKWave?

15:59 iverilog exe compiles the source files

16:06 vvp executable serves as the simulation runtime engine

16:59 How to create a verilog file using VSCode

19:56 module

20:17 half adder sample circuit using gate level modelling design

20:59 inputs

21:09 output ports

21:26 How to instantiate gates

23:23 How to write test bench

25:03 grave accent include compiler directive example

26:06 reg

26:53 How to declare output using wire keyword

29:43 How to code or set the values of inputs

30:03 timescale do not always default to 1 sec

31:26 How to save changes in dumpfile

32:06 vcd means value change dump

32:43 How to record top-level module wire signals using dumpvar

35:16 How to simulate vvp file

35:56 How to view or display the timing diagram using GTKWave

38:29 digital circuits with multiple gates, wires, netlist

00:23 Advantage of Textual Form Design

01:03 Altera HDL or AHDL

01:19 Just-Another HDL (JHDL)

01:33 VHSIC HDL (VHDL)

01:56 Meaning of VHSIC

02:30 Verilog

02:13 SystemVerilog

02:36 Test Bench

02:59 Logic Synthesis

03:06 Netlist

03:13 Verilog Modeling Styles

03:19 Gate-level Modeling

03:26 DataFlow Modeling

03:36 Behavioural Modeling

03:53 Verilog is case-sensitive just like C

04:06 White spaces, tabs, new lines are ignored

04:13 Keywords are lowercase

04:26 How to name a variable

04:36 System tasks or function starts with dollar sign

04:43 One line and multi-line comments

05:06 note on the old and new version of the syntax

05:13 module endmodule keyword pair

05:29 module name

05:33 port list

05:59 input and output keywords

06:19 Statements are terminated by semicolon

06:33 Icarus is Free and can be used offline

06:49 How to install iverilog

07:33 How to install Icarus for Windows

10:03 Where the verilog bin libraries or executables?

10:23 How to update PATH environment variables

11:46 How to check if iverilog is installed

11:56 How to view iverilog version

12:23 How to install Visual Studio Code Text Editor

14:06 How to customize or configure VS Code for Verilog

14:19 Verilog HDL extension

15:46 What is the purpose of GTKWave?

15:59 iverilog exe compiles the source files

16:06 vvp executable serves as the simulation runtime engine

16:59 How to create a verilog file using VSCode

19:56 module

20:17 half adder sample circuit using gate level modelling design

20:59 inputs

21:09 output ports

21:26 How to instantiate gates

23:23 How to write test bench

25:03 grave accent include compiler directive example

26:06 reg

26:53 How to declare output using wire keyword

29:43 How to code or set the values of inputs

30:03 timescale do not always default to 1 sec

31:26 How to save changes in dumpfile

32:06 vcd means value change dump

32:43 How to record top-level module wire signals using dumpvar

35:16 How to simulate vvp file

35:56 How to view or display the timing diagram using GTKWave

38:29 digital circuits with multiple gates, wires, netlist

Комментарии

0:04:40

0:04:40

0:14:50

0:14:50

0:04:30

0:04:30

0:10:50

0:10:50

0:07:01

0:07:01

0:42:03

0:42:03

0:53:59

0:53:59

0:05:30

0:05:30

0:32:28

0:32:28

0:33:54

0:33:54

0:05:35

0:05:35

0:34:01

0:34:01

0:01:00

0:01:00

0:18:59

0:18:59

0:03:06

0:03:06

0:13:35

0:13:35

0:49:20

0:49:20

0:12:10

0:12:10

0:12:08

0:12:08

0:19:31

0:19:31

0:09:35

0:09:35

0:00:38

0:00:38

0:51:31

0:51:31

0:49:20

0:49:20