filmov

tv

Introduction to FPGA Part 4 - Clocks and Procedural Assignments | Digi-Key Electronics

Показать описание

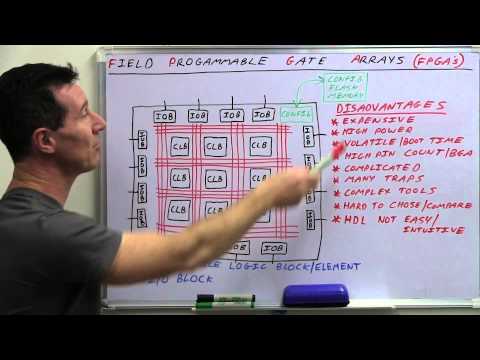

A field-programmable gate array (FPGA) is an integrated circuit (IC) that lets you implement custom digital circuits. You can use an FPGA to create optimized digital logic for things like digital signal processing (DSP), machine learning, and cryptocurrency mining. Because of the FPGA’s flexibility, you can often implement entire processors using its digital logic. You can find FPGAs in consumer electronics, satellites, and in servers used to perform specialized calculations.

In this series, we will see how an FPGA works and demonstrate how to create custom digital logic using the Verilog hardware description language (HDL).

We start by showing how the D flip-flop in an FPGA logic cell can be used to store a 1-bit value for one or (potentially) more clock cycles. Multiple D flip-flops can be combined with combinational logic gates to create hardware circuits that operate sequentially. We can control this sequential logic through Verilog blocks known as “procedural assignment statements.”

Next, we demonstrate a procedural assignment statement by constructing a simple 4-bit counter inside of an “always block.” Each time a button is pressed, the value increments by 1. The counter value is shown on the LEDs (in binary).

Note that you will likely experience button bounce that we have not accounted for in the demonstration. As a result, the counter will likely skip values each button press. You would need to implement button debounce circuitry (either in hardware or in HDL) to correct for this behavior. We will cover button debounce in a future episode.

Your challenge is to create a clock divider for the onboard 12 MHz oscillator (assuming you are using the iCEstick, the 12 MHz oscillator is connected to pin 21). The clock should be divided to 1 Hz, and this new clock signal should run the counter shown in the video. The new counter should increment on its own once per second.

Product Links:

Related Videos:

Related Project Links:

Related Articles:

Learn more:

In this series, we will see how an FPGA works and demonstrate how to create custom digital logic using the Verilog hardware description language (HDL).

We start by showing how the D flip-flop in an FPGA logic cell can be used to store a 1-bit value for one or (potentially) more clock cycles. Multiple D flip-flops can be combined with combinational logic gates to create hardware circuits that operate sequentially. We can control this sequential logic through Verilog blocks known as “procedural assignment statements.”

Next, we demonstrate a procedural assignment statement by constructing a simple 4-bit counter inside of an “always block.” Each time a button is pressed, the value increments by 1. The counter value is shown on the LEDs (in binary).

Note that you will likely experience button bounce that we have not accounted for in the demonstration. As a result, the counter will likely skip values each button press. You would need to implement button debounce circuitry (either in hardware or in HDL) to correct for this behavior. We will cover button debounce in a future episode.

Your challenge is to create a clock divider for the onboard 12 MHz oscillator (assuming you are using the iCEstick, the 12 MHz oscillator is connected to pin 21). The clock should be divided to 1 Hz, and this new clock signal should run the counter shown in the video. The new counter should increment on its own once per second.

Product Links:

Related Videos:

Related Project Links:

Related Articles:

Learn more:

Комментарии

0:18:09

0:18:09

0:24:24

0:24:24

0:20:44

0:20:44

0:11:01

0:11:01

0:15:21

0:15:21

0:11:51

0:11:51

0:34:11

0:34:11

0:12:31

0:12:31

2:17:01

2:17:01

0:01:26

0:01:26

0:04:44

0:04:44

0:08:46

0:08:46

0:16:35

0:16:35

0:00:34

0:00:34

0:05:42

0:05:42

0:27:03

0:27:03

0:18:51

0:18:51

0:37:44

0:37:44

0:17:36

0:17:36

0:04:59

0:04:59

0:23:06

0:23:06

0:22:34

0:22:34

0:36:06

0:36:06

0:12:28

0:12:28