filmov

tv

Introduction to Direct Memory Access (DMA)

Показать описание

#DMA #Xilinx #XAXIDMA

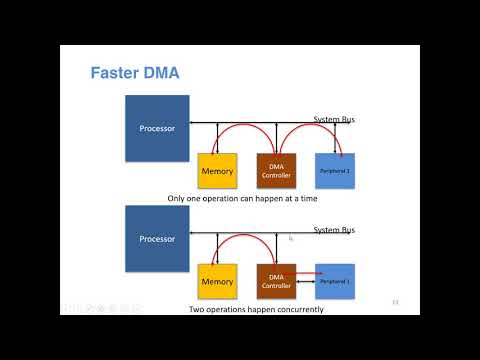

In this Video we will have a general over view of direct memory access (DMA). I will also introduce the Xilinx X_AXI_DMA IP core, which we will use in the subsequent tutorials. DMA is an important concept in developing high-speed hardware accelerators.

In this Video we will have a general over view of direct memory access (DMA). I will also introduce the Xilinx X_AXI_DMA IP core, which we will use in the subsequent tutorials. DMA is an important concept in developing high-speed hardware accelerators.

Introduction to Direct Memory Access (DMA)

Introduction to Direct Memory Access DMA

Introduction to Direct Memory Access (DMA)

Direct Memory Access - DMA - Simplified Explanation

Direct Memory Access - DMA (simplified)

Introduction to Direct Memory Access and CPU Bus Signals for DMA Transfer || Lesson 87 ||

What is DMA? What does it do? and Why is it Important?

Direct Memory Access

Simply Put: What is Direct Memory Access (DMA) in Embedded Systems

What is Direct Memory Access (DMA)? How disk controllers and memory communicate

Direct Memory Access (DMA): Working, IO Transfer Modes, and Timing Explained

What is DMA? Direct Memory Access Explained!! (SIMPLIFIED)

Direct Memory Access ( DMA ) Controller in Computer Organization Architecture || Modes of Transfer

Direct Memory Access(DMA) Controller #cse

Direct Memory Access (DMA)

Direct Memory Access - DMA - What it is and How To Use it To Your Advantage

Direct Memory Access | Working of DMA Controller | Computer Organisation and Architecture

COMPUTER ORGANIZATION | Part-25 | Direct Memory Access

Computer Organization #68: Full Concept of DMA | Direct Memory Access | DMA | Modes of DMA Transfer

8257 Direct Memory Access: Basics of DMA, HOLD, HLDA, and Working Mechanism

DIRECT MEMORY ACCESS (DMA)- Introduction and Concept

DIRECT MEMORY ACCESS [DMA]|DMA CONTROLLER|DMA TRANSFER

Direct Memory Access(DMA) || Introduction to Direct Memory Access || What is DMA || CO || CA || COA

8257 Direct Memory Access Controller (DMA) : Introduction

Комментарии

0:20:33

0:20:33

0:06:41

0:06:41

0:31:29

0:31:29

0:06:06

0:06:06

0:03:08

0:03:08

0:15:57

0:15:57

0:08:23

0:08:23

0:01:04

0:01:04

0:05:41

0:05:41

0:05:26

0:05:26

0:15:05

0:15:05

0:10:17

0:10:17

0:12:12

0:12:12

0:00:10

0:00:10

0:07:16

0:07:16

0:08:11

0:08:11

0:11:01

0:11:01

0:08:22

0:08:22

0:07:27

0:07:27

0:09:19

0:09:19

0:03:43

0:03:43

0:20:51

0:20:51

0:08:50

0:08:50

0:23:03

0:23:03