filmov

tv

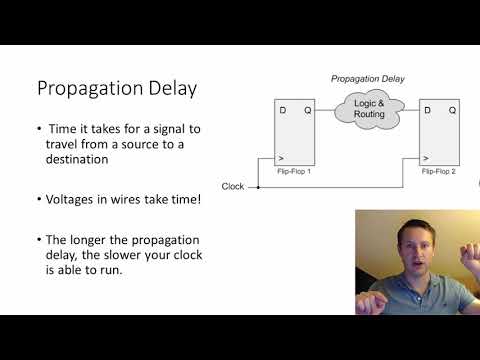

FPGA Clock and timing concepts explained simply for beginners using two analogies!

Показать описание

Hi, I'm Stacey and in this video I'll explain clock and timing concepts using two simple analogies:

The factory, and the stop motion movie!

Google form to give me your feedback:

Ending music: Faith by David van Niekerk

0:00 Intro

0:38 The factory: Intro

2:13 The factory: Timing analysis and closure

4:10 The factory: Strategies for meeting timing

5:02 The stop motion movie: Intro

5:52 The stop motion movie: Setup and hold times

7:08 Balancing combinitiorial logic and pipeline registers

The factory, and the stop motion movie!

Google form to give me your feedback:

Ending music: Faith by David van Niekerk

0:00 Intro

0:38 The factory: Intro

2:13 The factory: Timing analysis and closure

4:10 The factory: Strategies for meeting timing

5:02 The stop motion movie: Intro

5:52 The stop motion movie: Setup and hold times

7:08 Balancing combinitiorial logic and pipeline registers

FPGA Clock and timing concepts explained simply for beginners using two analogies!

Introduction to FPGA Part 10 - Metastability and Clock Domain Crossing | Digi-Key Electronics

Timing Constraints: How do I connect my top level source signals to pins on my FPGA?

Understanding Timing Analysis in FPGAs

What's an FPGA?

How to fix Timing Errors in your FPGA design during Place and Route, meeting clock constraints

INTRODUCTION TO SETUP AND HOLD TIMES | STA-1 | Static Timing Analysis

Setup, Hold, Propagation Delay, Timing Errors, Metastability in FPGA

Virtual Clock | Static Timing Analysis

FPGA Timing Optimization: Background and Challenges

What is a Clock in an FPGA?

Crossing Clock Domains in an FPGA

Basic Static Timing Analysis: Timing Concepts - Clocks

Synthesis/STA - virtual clock concept

FPGA Timing Optimization (Background and Challenges) _ OLD

Basic Static Timing Analysis: Timing Concepts - Timing Paths

METASTABILITY | RESOLUTION TIME | Static Timing Analysis | The Rising Edge

FPGA Timing Optimization: Background and Challenges OLD

LDC23 - FPGA Timing Constraints Deep Dive

FPGA Timing Optimization: Timer Example OLD

Xilinx® Training Global Timing Constraints

FPGA Timing Optimization (Background and Challenges) OLD

[Synthesis/STA] fixing setup and hold timing concepts

FPGA Timing Optimization: Optimization Strategies

Комментарии

0:08:51

0:08:51

0:13:26

0:13:26

0:07:29

0:07:29

0:29:41

0:29:41

0:01:26

0:01:26

0:14:00

0:14:00

0:06:51

0:06:51

0:11:08

0:11:08

0:04:18

0:04:18

0:22:53

0:22:53

0:18:58

0:18:58

0:16:38

0:16:38

0:20:37

0:20:37

0:08:20

0:08:20

0:22:11

0:22:11

0:15:18

0:15:18

0:07:27

0:07:27

0:22:53

0:22:53

1:04:19

1:04:19

0:14:24

0:14:24

0:27:46

0:27:46

0:22:50

0:22:50

![[Synthesis/STA] fixing setup](https://i.ytimg.com/vi/xEtPa_6B4SI/hqdefault.jpg) 0:11:31

0:11:31

0:42:39

0:42:39