filmov

tv

Dynamic CMOS ( Basics, Circuit, Working, Advantages & Disadvantages) Explained

Показать описание

Dynamic CMOS is explained with the following timecodes:

0:00 - VLSI Lecture Series

0:15 - Circuit of Dynamic CMOS

1:16 - How Dynamic CMOS is better compared to Static CMOS

3:45 - Dynamic CMOS Inverter

4:40 - Dynamic CMOS Inverter Working

12:10 - Advantages of Dynamic CMOS

13:55 - Disadvantages of Dynamic CMOS

Following points are covered in this video:

0. Complimentary Metal Oxide Semiconductor, CMOS

1. Dynamic CMOS

2. Basics of Dynamic CMOS

3. Number of transistors in Dynamic CMOS

4. Circuit of Dynamic CMOS

5. Working of Dynamic CMOS

Chapter-wise detailed Syllabus of the VLSI Course is as follows:

Evolution of Logic complexity, VLSI Design methodologies, Full Custom design and Semi Custom design, VLSI terminologies, Package Technology of IC, VLSI Design flow, Importance of CAD tools in VLSI, Comparison of FPGA, CPLD, PLC, DSP, Microcontroller and Microprocessor.

CMOS Fabrication process, Twin Tube CMOS Fabrication Process, Photolithography, Ion Implantation.

Two Terminal MOS structure, Flat band voltage, MOS under external bias, MOSFET, Threshold voltage of MOSFET, Gradual Channel Approximation of MOSFET, Channel Length Modulation of MOSFET, Substrate Bias Effect in MOSFET, MOSFET Capacitances, nMOS and pMOS, Examples on MOS, MOSFET, nMOS and pMOS.

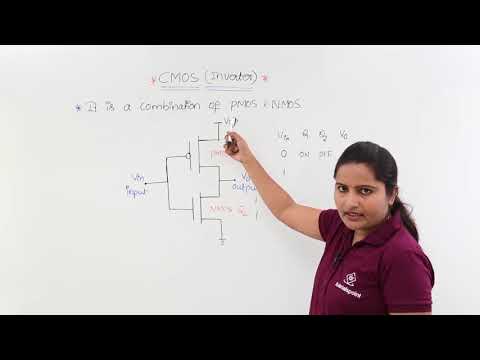

nMOS Inverter, Noise Margin and Transfer characteristics of nMOS Inverter, Resistive Load Inverter, Depletion Load nMOS Inverter, CMOS Inverter, Voltage Transfer characteristics of CMOS Inverter, Parameters of CMOS Inverter, Examples on CMOS Inverter, Propagation delay of CMOS Inverter.

CMOS Circuits rules, CMOS NAND gate, CMOS NOR gate, Boolean function using CMOS, CMOS Multiplexer, CMOS SR Latch using NOR gates, CMOS SR Latch using NAND gates, CMOS D Latch, CMOS SR Flip Flop using NOR gates, CMOS JK Flip Flop using NOR gates, Stick Diagram, CMOS Transmission Gate, Multiplexer using Transmission gates, D Latch using Transmission gates, Boolean function implementation using transmission gates.

Dynamic CMOS, Cascading issues of dynamic CMOS, Comparison of static CMOS and Dynamic CMOS, Domino Logic CMOS, Charge sharing in Dynamic CMOS, Boolean function implementation using dynamic CMOS, NORA CMOS logic, Boolean function implementation using NORA CMOS, Voltage Bootstrapping, Latch Up in CMOS and Latch up prevention steps, FinFET Technology.

On Chip Clock Generation, Ring Oscillator, Clock Distribution, Faults in Integrated circuits, BIST - Bult In Self Test in Integrated circuit, Stuck at Fault.

Engineering Funda channel is all about Engineering and Technology. Here this video is a part of VLSI.

#CMOS #VLSI #VlsiDesign @EngineeringFunda

0:00 - VLSI Lecture Series

0:15 - Circuit of Dynamic CMOS

1:16 - How Dynamic CMOS is better compared to Static CMOS

3:45 - Dynamic CMOS Inverter

4:40 - Dynamic CMOS Inverter Working

12:10 - Advantages of Dynamic CMOS

13:55 - Disadvantages of Dynamic CMOS

Following points are covered in this video:

0. Complimentary Metal Oxide Semiconductor, CMOS

1. Dynamic CMOS

2. Basics of Dynamic CMOS

3. Number of transistors in Dynamic CMOS

4. Circuit of Dynamic CMOS

5. Working of Dynamic CMOS

Chapter-wise detailed Syllabus of the VLSI Course is as follows:

Evolution of Logic complexity, VLSI Design methodologies, Full Custom design and Semi Custom design, VLSI terminologies, Package Technology of IC, VLSI Design flow, Importance of CAD tools in VLSI, Comparison of FPGA, CPLD, PLC, DSP, Microcontroller and Microprocessor.

CMOS Fabrication process, Twin Tube CMOS Fabrication Process, Photolithography, Ion Implantation.

Two Terminal MOS structure, Flat band voltage, MOS under external bias, MOSFET, Threshold voltage of MOSFET, Gradual Channel Approximation of MOSFET, Channel Length Modulation of MOSFET, Substrate Bias Effect in MOSFET, MOSFET Capacitances, nMOS and pMOS, Examples on MOS, MOSFET, nMOS and pMOS.

nMOS Inverter, Noise Margin and Transfer characteristics of nMOS Inverter, Resistive Load Inverter, Depletion Load nMOS Inverter, CMOS Inverter, Voltage Transfer characteristics of CMOS Inverter, Parameters of CMOS Inverter, Examples on CMOS Inverter, Propagation delay of CMOS Inverter.

CMOS Circuits rules, CMOS NAND gate, CMOS NOR gate, Boolean function using CMOS, CMOS Multiplexer, CMOS SR Latch using NOR gates, CMOS SR Latch using NAND gates, CMOS D Latch, CMOS SR Flip Flop using NOR gates, CMOS JK Flip Flop using NOR gates, Stick Diagram, CMOS Transmission Gate, Multiplexer using Transmission gates, D Latch using Transmission gates, Boolean function implementation using transmission gates.

Dynamic CMOS, Cascading issues of dynamic CMOS, Comparison of static CMOS and Dynamic CMOS, Domino Logic CMOS, Charge sharing in Dynamic CMOS, Boolean function implementation using dynamic CMOS, NORA CMOS logic, Boolean function implementation using NORA CMOS, Voltage Bootstrapping, Latch Up in CMOS and Latch up prevention steps, FinFET Technology.

On Chip Clock Generation, Ring Oscillator, Clock Distribution, Faults in Integrated circuits, BIST - Bult In Self Test in Integrated circuit, Stuck at Fault.

Engineering Funda channel is all about Engineering and Technology. Here this video is a part of VLSI.

#CMOS #VLSI #VlsiDesign @EngineeringFunda

Комментарии

0:15:34

0:15:34

0:13:01

0:13:01

0:12:12

0:12:12

0:13:25

0:13:25

0:12:20

0:12:20

0:12:45

0:12:45

0:12:55

0:12:55

0:10:14

0:10:14

0:10:44

0:10:44

0:07:50

0:07:50

0:09:47

0:09:47

0:07:55

0:07:55

0:14:13

0:14:13

0:04:55

0:04:55

0:49:25

0:49:25

0:09:44

0:09:44

0:17:30

0:17:30

0:12:57

0:12:57

0:07:06

0:07:06

0:28:11

0:28:11

0:36:19

0:36:19

0:04:57

0:04:57

0:11:31

0:11:31

0:05:47

0:05:47