filmov

tv

Multiplication Algorithm | Signed Magnitude Data || Computer Organization and Architecture

Показать описание

#architecture #organization #cao #coa #kcs302 #aktu #sapnakatiyar #multiplication #algorithm #hardware #implementation #flowchart #example

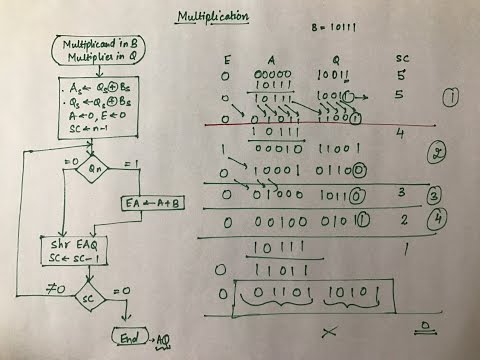

This video lecture is about the Multiplication Algorithm for Signed Magnitude Data. Multiplication of two fixed point binary number in signed magnitude representation is done with process of successive shift and add operation.

Hardware Implementation for Multiply Operation has been discussed.

Hardware Algorithm for Multiply Operation has also been discussed in detail along with Flow Chart. An example for multiplication is also discussed in detail.

Please like, subscribe and share if you like the video.

This channel is providing the complete lecture series of following Subjects:

1. Digital Image Processing

2. Satellite Communication

3. Electronic Devices

4. Communication Engineering

5. Cloud Computing

6. Radar Systems

7. Digital & Social Media Marketing

8. Digital Image Processing - Multiple Choice Questions (MCQs)

9. Satellite Communication - Multiple Choice Questions (MCQs)

10. Radar Systems - Multiple Choice Questions (MCQs)

11. Communication Engineering - Multiple Choice Questions (MCQs)

This video lecture is about the Multiplication Algorithm for Signed Magnitude Data. Multiplication of two fixed point binary number in signed magnitude representation is done with process of successive shift and add operation.

Hardware Implementation for Multiply Operation has been discussed.

Hardware Algorithm for Multiply Operation has also been discussed in detail along with Flow Chart. An example for multiplication is also discussed in detail.

Please like, subscribe and share if you like the video.

This channel is providing the complete lecture series of following Subjects:

1. Digital Image Processing

2. Satellite Communication

3. Electronic Devices

4. Communication Engineering

5. Cloud Computing

6. Radar Systems

7. Digital & Social Media Marketing

8. Digital Image Processing - Multiple Choice Questions (MCQs)

9. Satellite Communication - Multiple Choice Questions (MCQs)

10. Radar Systems - Multiple Choice Questions (MCQs)

11. Communication Engineering - Multiple Choice Questions (MCQs)

Multiplication Algorithm With Signed Magnitude Data In Computer Organization Architecture

Multiplication ( Binary Arithmetic ) - Part 2

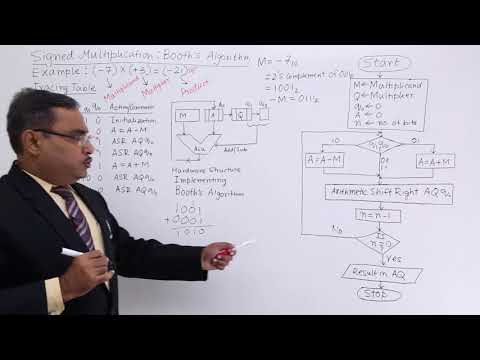

Booth's Algorithm for Signed Multiplication

Multiplication Algorithm | Signed Magnitude Data || Computer Organization and Architecture

Multiplication Algorithm for signed magnitude data

Binary Multiplication of Signed Numbers | 2s Complement Binary Multiplication

Flowchart with example of multiplication of two signed magnitude fixed point numbers-lecture34/coa

23 multiplication using signed magnitude

Multiplication Using Add Shift Method

booths algoritham in computer organization| multiplication | COA

The Concept of Booth’s Algorithm

COA14: Multiplication: Signed Operand Multiplication | Multiplication Algorithm | Signed Magnitude

Signed Magnitude Representation

Booth's Algorithm With Example | booths | booths algo

''Multiplication Algorithm in Signed Magnitude Representation'' Computer Organiz...

Binary Multiplication with example

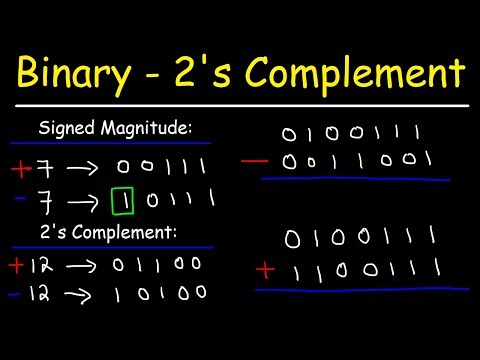

Binary Addition and Subtraction With Negative Numbers, 2's Complements & Signed Magnitude

Signed magnitude multiplication

Hardware implementation of multiplication of two signed magnitude numbers-lecture33/coa

Multiplication Algorithm || Flowchart for Multiplication Algorithm with Example || CO || COA ||

Booth Multiplication algorithm with example || Multiplication with signed 2's complement data |...

Division Algorithm In Computer Organization Architecture || Restoring Algorithm | Signed Magnitude

Representation of signed number | sign magnitude form | 1's complement and 2's complement...

Block diagram of addition and subtraction with signed magnitude

Комментарии

0:18:17

0:18:17

0:06:01

0:06:01

0:14:32

0:14:32

0:15:05

0:15:05

0:40:31

0:40:31

0:14:14

0:14:14

0:09:37

0:09:37

0:04:22

0:04:22

0:11:00

0:11:00

0:12:25

0:12:25

0:11:51

0:11:51

0:27:40

0:27:40

0:05:31

0:05:31

0:07:29

0:07:29

0:23:49

0:23:49

0:08:04

0:08:04

0:24:57

0:24:57

0:08:55

0:08:55

0:06:01

0:06:01

0:28:19

0:28:19

0:18:57

0:18:57

0:27:24

0:27:24

0:05:56

0:05:56

0:00:05

0:00:05