filmov

tv

how does a Mutex even work? (atoms in the computer??)

Показать описание

Thread synchronization is easier said then done. If you use a library like pthread for multithreading and mutexes, then you're probably going to be okay. But, if you're writing your own RTOS, figuring out how mutexes work under the hood is really important.

Mutexes work under the hood in your OS using atomic operations on the computer processor. Atomic Operations are operations on the CPU that cannot be interrupted and are therefore immune to a race condition.

🔥🔥🔥 SOCIALS 🔥🔥🔥

Mutexes work under the hood in your OS using atomic operations on the computer processor. Atomic Operations are operations on the CPU that cannot be interrupted and are therefore immune to a race condition.

🔥🔥🔥 SOCIALS 🔥🔥🔥

how does a Mutex even work? (atoms in the computer??)

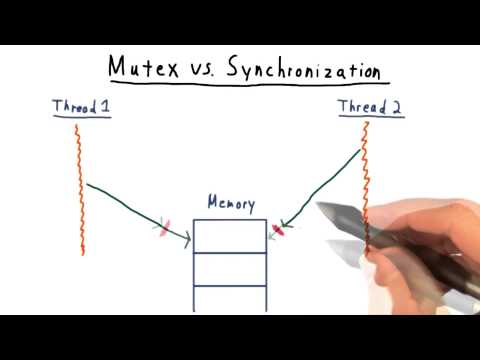

Mutex vs Synchronization

What is a mutex in C? (pthread_mutex)

Mutex Introduction (pthreads) | C Programming Tutorial

What is a Mutex? How does it work?

What is Mutex in C++ (Multithreading for Beginners)

FANG Interview Question | Process vs Thread

Recursive mutexes

Thread synchronization with mutexes in C

What's Spin Lock? Spin Lock Vs. Mutex.

OS30 - Mutex Lock

Mutex in golang

Goroutines Crash Course (Mutex, Channels, Wait Group, & More!)

Introduction to RTOS Part 6 - Mutex | Digi-Key Electronics

C# Mutex/Lock Multithreading/tasks

Exploring Mutex Locks and Latency in Computer Science

std::mutex and preventing data races in C++ | Introduction to Concurrency in Cpp

Concurrency in Rust - Sharing State

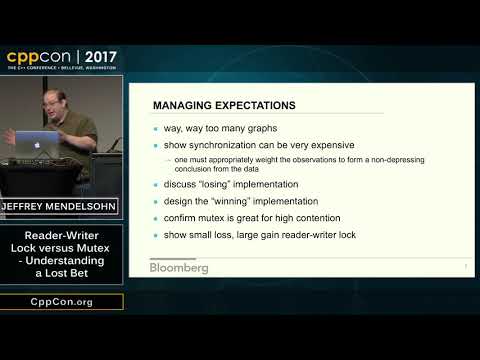

CppCon 2017: Jeffrey Mendelsohn “Reader-Writer Lock versus Mutex - Understanding a Lost Bet”

Modern C++ - Parallelismus und Concurrency #2 - Mutex

Why Mutex/Locking is Required - Explained | Multi-Threading | Thread Synchronization

SAFE Multithreading with Mutex Locks

C++ From Scratch: std::mutex

What is a mutex in concurrent programming?#mutex#concurrent#programming

Комментарии

0:04:17

0:04:17

0:00:53

0:00:53

0:09:18

0:09:18

0:10:19

0:10:19

0:01:04

0:01:04

0:12:29

0:12:29

0:03:51

0:03:51

0:07:06

0:07:06

0:05:21

0:05:21

0:05:07

0:05:07

0:09:53

0:09:53

0:05:41

0:05:41

0:15:42

0:15:42

0:13:44

0:13:44

0:07:17

0:07:17

0:01:00

0:01:00

0:12:46

0:12:46

0:09:12

0:09:12

0:42:01

0:42:01

0:13:12

0:13:12

0:06:42

0:06:42

0:07:51

0:07:51

0:10:33

0:10:33

0:00:21

0:00:21