filmov

tv

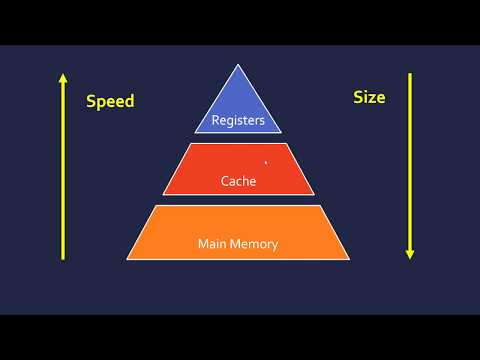

Differences between Cache and Registers (Computer Architecture)

Показать описание

Check this video to know the differences between cache memory and registers!

Link to other videos:

LIKE and SHARE the video.

Comment down your answers.

SUBSCRIBE to the channel!

You can find me on:

Cheers!

#computerarchitecture #cache #coa #computermemory

Link to other videos:

LIKE and SHARE the video.

Comment down your answers.

SUBSCRIBE to the channel!

You can find me on:

Cheers!

#computerarchitecture #cache #coa #computermemory

Differences between Cache and Registers (Computer Architecture)

Explain? registers and cache.

What is Cache Memory? L1, L2, and L3 Cache Memory Explained

Computer Architecture - Cache & Registers

WHICH IS BETTER |REGISTER VS CACHE MEMORY #computer #gk #shorts

Registers and RAM: Crash Course Computer Science #6

How computer memory works - Kanawat Senanan

Understanding the Distinction Between Cache Memory and Registers

Overview of computer memory ∣ RAM, Cache, Register, HDD | Memory organisation

Difference between cache memory and register? (6 Solutions!!)

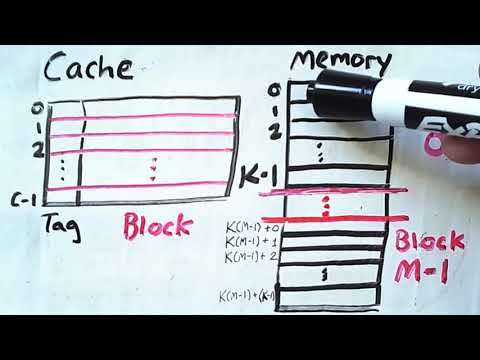

Cache and Registers

CPU Cache Explained - What is Cache Memory?

Main Memory (RAM, ROM and Cache)

Introduction to Memory

Cache Memory Explained

RAM Vs. ROM | Animation

How Cache Works In Computers to Speed Up the CPU

cache memory in computer architecture

Register memory II Cache memory II Difference between register and cache memory II

Introduction to Cache Memory Concepts

Difference Between L1 L2 and L3 Cache Memory

How a CPU Works in 100 Seconds // Apple Silicon M1 vs Intel i9

What is Cache Memory ? | How Cache memory is different from primary memory and registers

Diff. between cache memory and register memory in Tamil / Meaning of Cache memory & Register mem...

Комментарии

0:06:15

0:06:15

0:01:28

0:01:28

0:01:58

0:01:58

0:02:34

0:02:34

0:01:01

0:01:01

0:12:17

0:12:17

0:05:05

0:05:05

0:01:35

0:01:35

0:04:48

0:04:48

0:02:58

0:02:58

0:05:21

0:05:21

0:04:51

0:04:51

0:08:22

0:08:22

0:07:46

0:07:46

0:07:00

0:07:00

0:07:00

0:07:00

0:05:27

0:05:27

0:07:33

0:07:33

0:14:29

0:14:29

0:07:31

0:07:31

0:01:19

0:01:19

0:12:44

0:12:44

0:01:54

0:01:54

0:05:10

0:05:10