filmov

tv

Chip floorplanning with deep reinforcement learning

Показать описание

Learn about a deep reinforcement learning method that can generate superhuman chip layouts in under six hours, rather than weeks or months of human effort. This method was recently published in Nature and was used in production to generate chip layouts for Google’s latest AI accelerator (TPU).

Speakers:

Anna Goldie (Staff Research Scientist), Azalia Mirhoseini (Staff Research Scientist)

#MLCommunityDay

product: TensorFlow - General; event: ML Community Day 2021; fullname: Anna Goldie, Azalia Mirhoseini; re_ty: Publish;

Speakers:

Anna Goldie (Staff Research Scientist), Azalia Mirhoseini (Staff Research Scientist)

#MLCommunityDay

product: TensorFlow - General; event: ML Community Day 2021; fullname: Anna Goldie, Azalia Mirhoseini; re_ty: Publish;

Chip floorplanning with deep reinforcement learning

Chip Placement with Deep Reinforcement Learning (Paper Explained)

M4LA 2021 - Anna Goldie - Model Parallelism and Chip Floorplanning with Deep Reinforcement Learning

Chip Placement with Deep Reinforcement Learning | Paper Explained

Reinforcement Learning for Hardware Design feat. Anna Goldie | Stanford MLSys Seminar Episode 14

Google brain - AI Chip development for floor planning

Chip Placement with Deep Reinforcement Learning #4

Keynote: ML for Systems and Chip Design - Azalia Mirhoseini, Senior Research Scientist, Google Brain

Chip Placement with Deep Reinforcement Learning #3

Deep Reinforcement Learning: Field Development Optimization | Paper Explained

Google’s AI chief explains machine learning for chip design

New AI Learned to Design Computer Chips: The View of a Chip Designer

Google-KI übertrifft jeden Menschen in Chipentwicklung

Google’s Chip Designing AI

Machine-Learning Optimized Chip Design -- Cadence Design Systems

Device Placement Optimization with Reinforcement Learning

Reinforcement learning for chip design

Build a board game app with policy gradient (Reinforcement learning with TensorFlow Agents)

AI-agents Trained using Deep Reinforcement Learning in the CARLA Simulator

The Impact Of Machine Learning On Chip Design

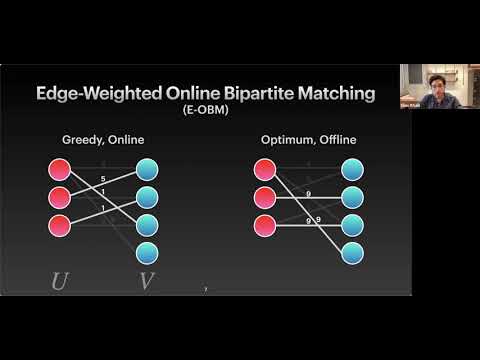

Deep Reinforcement Learning for Online Combinatorial Optimization: The Case of Bipartite Matching

【Research 01】My research on transition control based on multi-agent deep reinforcement learning

Device Placement Optimisation with Reinforcement Learning

State-of-the-art Machine Learning research with Google tools | Keynote

Комментарии

0:09:33

0:09:33

0:27:27

0:27:27

0:35:26

0:35:26

0:35:41

0:35:41

0:57:26

0:57:26

0:00:30

0:00:30

0:31:52

0:31:52

0:19:37

0:19:37

0:23:10

0:23:10

0:10:38

0:10:38

0:01:14

0:01:14

0:12:46

0:12:46

0:07:22

0:07:22

0:13:18

0:13:18

0:17:47

0:17:47

0:21:35

0:21:35

0:44:35

0:44:35

0:06:11

0:06:11

0:16:07

0:16:07

0:17:03

0:17:03

0:59:25

0:59:25

0:23:19

0:23:19

0:22:11

0:22:11

0:03:41

0:03:41