filmov

tv

Packaging Part 5 - Manufacturing process

Показать описание

References:

[3] Protected chip pic18f6525 heximal reading from its flash. (2019, June 26). Retrieved March 01, 2021

[5] Tsai, Jinn-Tsong & Chang, Cheng-Chung & Chen, Wen-Ping & Chou, Jyh-Horng. (2016). Optimal Parameter Design for IC Wire Bonding Process by Using Fuzzy Logic and Taguchi Method. IEEE Access. 4. 1-1. 10.1109/ACCESS.2016.2581258.

[15] Paquet, M., Dufort, C., Lombardi, T., Sinha, T., Hasegawa, M., Okoshi, K., & Kohara, K. (2016). Effect of Underfill Formulation on Large-Die, Flip-Chip Organic Package Reliability: A Systematic Study on Compositional and Assembly Process Variations. 2016 IEEE 66th Electronic Components and Technology Conference (ECTC), 729-736.

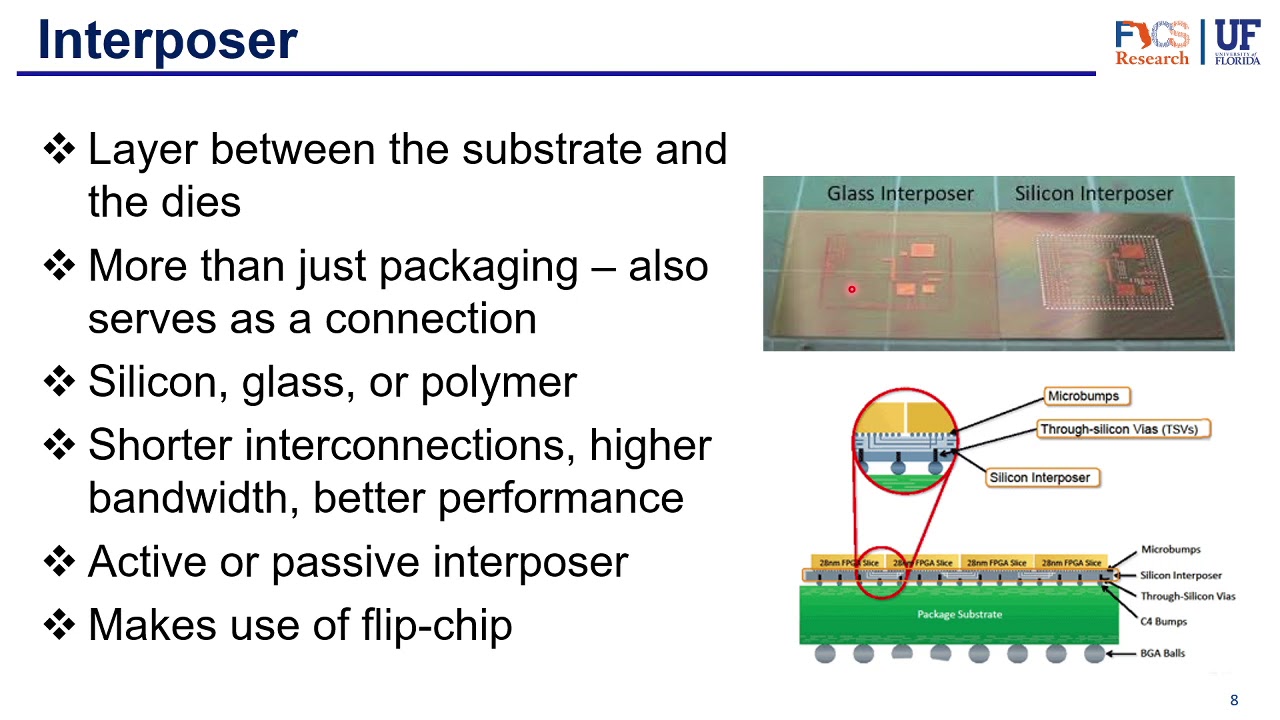

[17] C. Chien et al., "Performance and process characteristic of glass interposer with through-glass-via(TGV)," 2013 IEEE International 3D Systems Integration Conference (3DIC), San Francisco, CA, USA, 2013, pp. 1-7, doi: 10.1109/3DIC.2013.6702380.

[18] Saban, K. (2009). Xilinx Stacked Silicon Interconnect Technology Delivers Breakthrough FPGA Capacity , Bandwidth , and Power Efficiency.

[21] P. A. Thadesar, X. Gu, R. Alapati and M. S. Bakir, "Through-Silicon Vias: Drivers, Performance, and Innovations," in IEEE Transactions on Components, Packaging and Manufacturing Technology, vol. 6, no. 7, pp. 1007-1017, July 2016, doi: 10.1109/TCPMT.2016.2524691.

[3] Protected chip pic18f6525 heximal reading from its flash. (2019, June 26). Retrieved March 01, 2021

[5] Tsai, Jinn-Tsong & Chang, Cheng-Chung & Chen, Wen-Ping & Chou, Jyh-Horng. (2016). Optimal Parameter Design for IC Wire Bonding Process by Using Fuzzy Logic and Taguchi Method. IEEE Access. 4. 1-1. 10.1109/ACCESS.2016.2581258.

[15] Paquet, M., Dufort, C., Lombardi, T., Sinha, T., Hasegawa, M., Okoshi, K., & Kohara, K. (2016). Effect of Underfill Formulation on Large-Die, Flip-Chip Organic Package Reliability: A Systematic Study on Compositional and Assembly Process Variations. 2016 IEEE 66th Electronic Components and Technology Conference (ECTC), 729-736.

[17] C. Chien et al., "Performance and process characteristic of glass interposer with through-glass-via(TGV)," 2013 IEEE International 3D Systems Integration Conference (3DIC), San Francisco, CA, USA, 2013, pp. 1-7, doi: 10.1109/3DIC.2013.6702380.

[18] Saban, K. (2009). Xilinx Stacked Silicon Interconnect Technology Delivers Breakthrough FPGA Capacity , Bandwidth , and Power Efficiency.

[21] P. A. Thadesar, X. Gu, R. Alapati and M. S. Bakir, "Through-Silicon Vias: Drivers, Performance, and Innovations," in IEEE Transactions on Components, Packaging and Manufacturing Technology, vol. 6, no. 7, pp. 1007-1017, July 2016, doi: 10.1109/TCPMT.2016.2524691.

Комментарии

0:19:04

0:19:04

0:02:41

0:02:41

0:00:36

0:00:36

0:00:10

0:00:10

0:03:22

0:03:22

0:15:55

0:15:55

0:02:50

0:02:50

0:00:51

0:00:51

0:00:21

0:00:21

0:02:12

0:02:12

0:00:13

0:00:13

0:00:13

0:00:13

0:00:45

0:00:45

0:00:44

0:00:44

0:00:13

0:00:13

0:00:13

0:00:13

0:00:26

0:00:26

0:00:16

0:00:16

0:00:14

0:00:14

0:00:27

0:00:27

0:00:13

0:00:13

0:00:11

0:00:11

0:00:31

0:00:31

0:00:24

0:00:24