filmov

tv

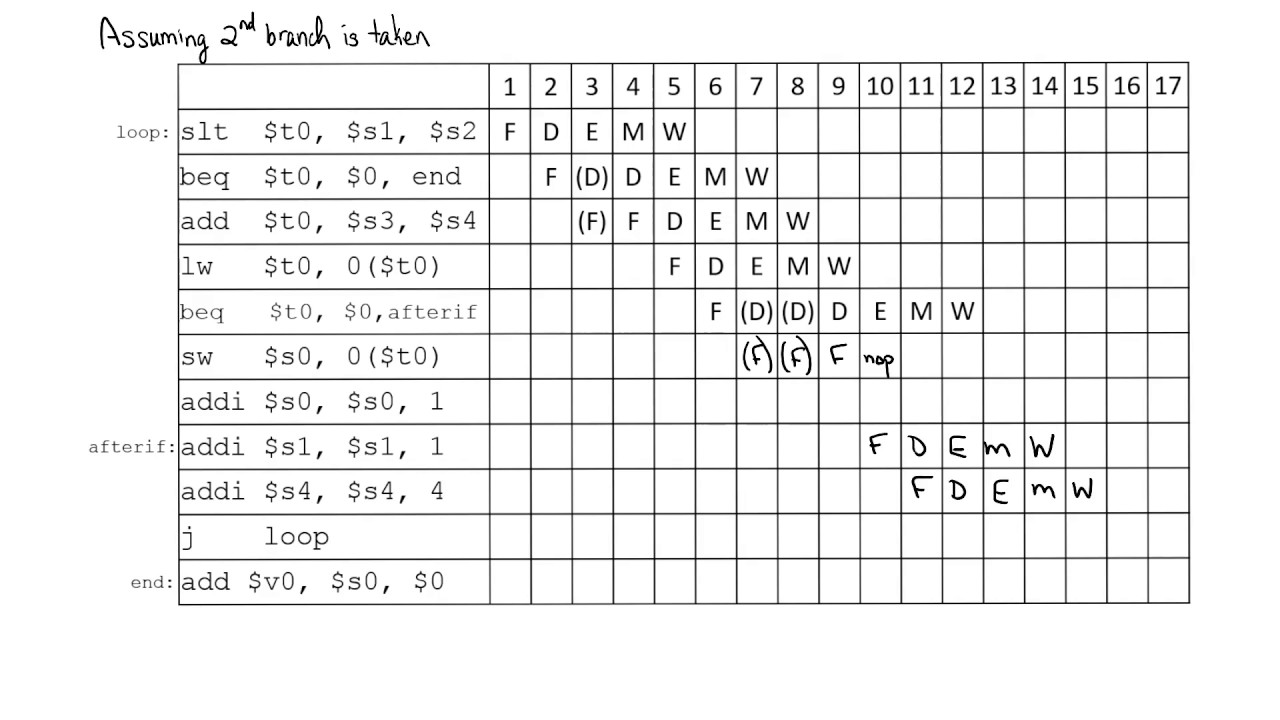

5-Stage Pipeline Processor Execution Example

Показать описание

Discusses how a set of instructions would execute through a classic MIPS-like 5-stage pipelined processor. Also looks at calculating the average CPI for the instruction sequence.

NOTE: This example assumes there is *NO* branch delay slot.

NOTE: This example assumes there is *NO* branch delay slot.

5-Stage Pipeline Processor Execution Example

5 Stage Pipeline

5-Stage Pipeline Processor Execution Example (v1.1)

Tutorial 5 part 3 (Pipe-lining)

1 3 1 Pipelining Principles

L-4.2: Pipelining Introduction and structure | Computer Organisation

1 3 2 Canonical 5 Stage Pipeline

1 3 4 Structural Hazards&Data Hazards

L7 5 mips pipeline walkthrough

Pipeline in ARM Processors (3,5 stage)

Computer Architecture: Pipeline and Non pipeline Comparision Problem

Instruction Pipeline Design - ACA

15.2.2 Basic 5-Stage Pipeline

Instruction Pipeline In Computer Organization Architecture || Pipelining

Stages in Pipeline

hazards practice problem solutoins

Pipeline Architecture GATE Exercise 1

Instruction Pipelining: Stages & Numericals

Synchronous Pipeline processor/computer Architecture design

4 5 Stage Pipeline Analysis Computer Organization

1. Introdution to the 5-Stage Pipeline

Introduction to Pipeline Architecture

DDCA Ch7 - Part 13: Pipelined Processor

Pipelining in COA: Examples, Instruction Pipelining and Solved Problems - 5 | COA

Комментарии

0:15:37

0:15:37

0:06:25

0:06:25

0:15:38

0:15:38

0:09:58

0:09:58

0:06:45

0:06:45

0:03:54

0:03:54

0:14:49

0:14:49

0:10:36

0:10:36

0:06:55

0:06:55

0:19:56

0:19:56

0:14:38

0:14:38

0:10:11

0:10:11

0:07:02

0:07:02

0:09:53

0:09:53

0:15:48

0:15:48

0:11:01

0:11:01

0:06:46

0:06:46

0:09:46

0:09:46

0:05:26

0:05:26

0:00:51

0:00:51

0:02:37

0:02:37

0:14:31

0:14:31

0:11:26

0:11:26

0:17:10

0:17:10