filmov

tv

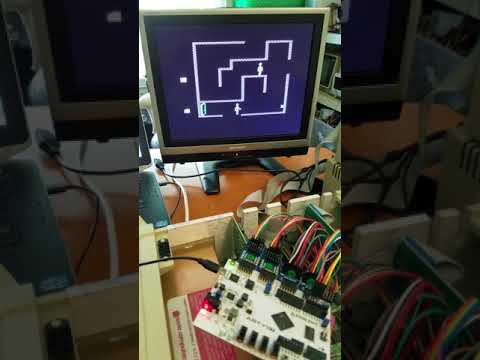

FPGA 6502: Implement 'ROL abs' part 3 of 3

Показать описание

We finally start implementing an actual opcode. This is part 3 of 3, in which set the control lines (microcode) for updating the status flags.

We also encounter a bug in the CPU design.

Project CompuSAR aims at building 70's and 80's computers on a low-end FPGA. Most of the project works from scratch, and this channel half documents the progress, half teaches about the concepts that come into play when designing such a system.

External links:

Music:

Licensed under Creative Commons: By Attribution 4.0 License

Table of contents:

00:00 Intro

00:26 Test driven development

01:17 Update the test plan

05:46 Running the test

06:54 Implement the Carry

09:08 Run test

10:05 Problem in our CPU design

12:40 Deciding on a solution

16:44 Solution reached

18:16 Verify solution

19:48 Updating N and Z flags

25:31 Wrap up

We also encounter a bug in the CPU design.

Project CompuSAR aims at building 70's and 80's computers on a low-end FPGA. Most of the project works from scratch, and this channel half documents the progress, half teaches about the concepts that come into play when designing such a system.

External links:

Music:

Licensed under Creative Commons: By Attribution 4.0 License

Table of contents:

00:00 Intro

00:26 Test driven development

01:17 Update the test plan

05:46 Running the test

06:54 Implement the Carry

09:08 Run test

10:05 Problem in our CPU design

12:40 Deciding on a solution

16:44 Solution reached

18:16 Verify solution

19:48 Updating N and Z flags

25:31 Wrap up

FPGA 6502: Implement 'ROL abs' part 1 of 3

FPGA 6502: Implement 'ROL abs' part 2 of 3

FPGA 6502: Implement 'ROL abs' part 3 of 3

FPGA 6502: Implement 'ROL' part 4 of 3

MCL65 6502 FPGA core running Zaxxon on Apple II+

hello world from scratch on a 6502 FPGA core

MCL65 6502 FPGA core running Frogger on Atari 2600

Finalizing the CPU

MCL65 6502 FPGA core running Castle Wolfenstein on Apple II+

Timing diagrams in practice: connecting 6502 to SRAM

Building 65c02 from scratch in Verilog: Why on earth???

Timing diagrams: Opcode control lines timing.

Bootable 6502 processor simulator I/O handling

Visual 6502

Emulating a CPU in C++ #27 (6502) - Arithmetic Shift Left

Building a 6800 CPU on an FPGA with nMigen (part 9)

Making an ALU for my TTL 6502 CPU - part 1

Jeft Tranter Thank you...65c02 board test ok - loading and saving

Western Design Center: How Telephones turned into the 65C02, and the 65C816 story — Bil Mensch

What is an FPGA? - FPGA Basics Episode 1

Understanding of a W65C02 micro computer

Building a 6800 CPU on an FPGA with nMigen (part 4)

8Bit Breadboard Computer mit 6502, Evolution von Maschinensprache zu Assembler

xilinx fpga tutorial part 2

Комментарии

0:21:29

0:21:29

0:18:56

0:18:56

0:27:02

0:27:02

0:18:43

0:18:43

0:00:35

0:00:35

0:00:51

0:00:51

0:00:47

0:00:47

0:12:53

0:12:53

0:01:08

0:01:08

0:32:05

0:32:05

0:28:43

0:28:43

0:20:54

0:20:54

0:26:23

0:26:23

0:01:13

0:01:13

0:18:57

0:18:57

0:58:36

0:58:36

0:20:23

0:20:23

0:00:37

0:00:37

1:33:42

1:33:42

0:50:40

0:50:40

0:02:58

0:02:58

1:03:01

1:03:01

0:52:15

0:52:15

0:34:43

0:34:43