filmov

tv

Why DFE?

Показать описание

The Decision-Feedback Equalizer (DFE) is one kind of equalizers in communication system. To provide an intuitive image, we went through other equalizers' limitation and emphasize the DFE's strength images such that everyone can follow the needs of DFE easily.

Why DFE?

What is a Decision Feedback Equalizer (DFE)?

Why NOT DFE-Only?

Why Floating-tap or Dual-summer in A DFE?

Why Does DFE Use a Triangular Filter?

Meet Oyin - An Economic Advisor at DFE

High Speed Communications Part 3 – Equalization & MLSD

EyeKnowHow: DDR5: DFE Features in Serial Interface vs. Memory Interface Innovations in Technology

Working Together on Workload

Meet Jess - An Economist at DFE

Filtering v monitoring - what's the difference (KCSIE & DfE Filtering Standards)

ALS oder WIE? Was ist eigentlich das Problem?

The Flash becomes faster than time itself #theflash

GEL7114 - Module 4.9 - Decision Feedback Equalizer (DFE)

Decision Feedback Equalization

DFE - Decision Feedback Equalizer | Nachrichtentechnik

How are Different Equalization Methods Related? (DFE, ZF, MMSE, Viterbi, OFDM)

GET £10000K RELOCATING TO THE UK AS A SECONDARY SCHOOL TEACHER #vivianoseni #teachinginuk #ukvisa

Why Not DFE or Only-1tap Digital DFE in ADC-DSP RX?

Together we can tackle child abuse

Complaining to the DfE

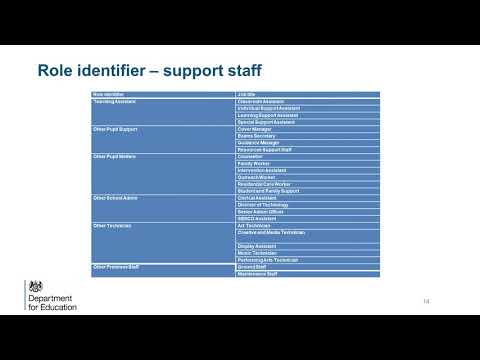

DfE School Workforce

Why Half-Rate or Quarter-Rate RX DFE?

Introducing Zynq® RFSoC DFE

Комментарии

0:12:49

0:12:49

0:10:49

0:10:49

0:16:48

0:16:48

0:17:57

0:17:57

0:00:19

0:00:19

0:01:48

0:01:48

0:06:12

0:06:12

0:14:40

0:14:40

0:03:38

0:03:38

0:01:43

0:01:43

0:01:55

0:01:55

0:00:41

0:00:41

0:00:32

0:00:32

0:08:06

0:08:06

0:10:14

0:10:14

0:11:18

0:11:18

0:20:24

0:20:24

0:00:15

0:00:15

0:13:07

0:13:07

0:00:30

0:00:30

0:06:49

0:06:49

0:18:57

0:18:57

0:13:17

0:13:17

0:01:46

0:01:46