filmov

tv

FSK Modulation and Demodulation

Показать описание

An explanation about FSK Modulation and Demodulation.

In this video, Gregory explains the full topology of an FSK demodulator, showing how the bitstream is recovered, how time is synchronized and frequencies offset are compensated.

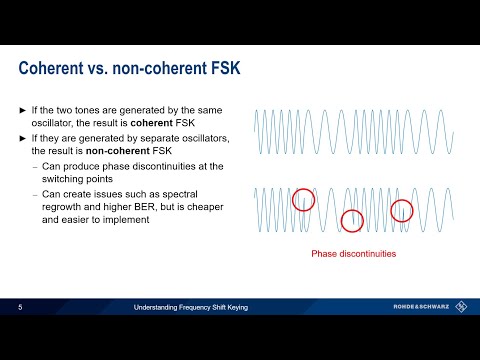

FSK modulation encodes the data in shifts of frequency. In the case of binary signaling, two different frequencies are used, representing 0 and 1.

The process of demodulation is done using two NCOs - Numeric Controlled Oscillators - and average filters, actually implementing a sample-by-sample DFT in real-time.

The energies at the two different frequencies are compared to determine if the data bit is a 1 or a 0.

The continuous recovered bitstream is sampled with a NCO running at the baudrate and a Gardner Time Error Detector in conjunction with a PI controller corrects the sampling interval/point.

Frequency offset are compensated using a slow time-constant servo-loop that equalize average energy of the sampled points.

Support the channel, become a Patron!

A related video about Clock Recovery PLL:

Learn how a Costas Loop demodulator works for PSK modulations:

Article about how DFT works:

00:18 - Introduction

03:36 - Overall demodulator topology

06:15 - Detecting energy without filter (DFT)

10:38 - Quadrature detection topology

13:24 - Time Recovery/Synchronization

16:55 - Offset compensation/Carrier Recovery

Subscribe to receive more videos.

In this video, Gregory explains the full topology of an FSK demodulator, showing how the bitstream is recovered, how time is synchronized and frequencies offset are compensated.

FSK modulation encodes the data in shifts of frequency. In the case of binary signaling, two different frequencies are used, representing 0 and 1.

The process of demodulation is done using two NCOs - Numeric Controlled Oscillators - and average filters, actually implementing a sample-by-sample DFT in real-time.

The energies at the two different frequencies are compared to determine if the data bit is a 1 or a 0.

The continuous recovered bitstream is sampled with a NCO running at the baudrate and a Gardner Time Error Detector in conjunction with a PI controller corrects the sampling interval/point.

Frequency offset are compensated using a slow time-constant servo-loop that equalize average energy of the sampled points.

Support the channel, become a Patron!

A related video about Clock Recovery PLL:

Learn how a Costas Loop demodulator works for PSK modulations:

Article about how DFT works:

00:18 - Introduction

03:36 - Overall demodulator topology

06:15 - Detecting energy without filter (DFT)

10:38 - Quadrature detection topology

13:24 - Time Recovery/Synchronization

16:55 - Offset compensation/Carrier Recovery

Subscribe to receive more videos.

Комментарии

0:21:25

0:21:25

0:08:55

0:08:55

0:25:58

0:25:58

0:05:30

0:05:30

0:06:49

0:06:49

0:16:13

0:16:13

0:28:20

0:28:20

0:07:26

0:07:26

0:17:45

0:17:45

0:06:25

0:06:25

0:11:56

0:11:56

0:10:54

0:10:54

0:12:00

0:12:00

0:01:25

0:01:25

0:03:51

0:03:51

0:09:43

0:09:43

0:10:03

0:10:03

0:21:25

0:21:25

0:03:31

0:03:31

0:00:38

0:00:38

0:19:37

0:19:37

0:01:01

0:01:01

0:26:04

0:26:04

0:28:01

0:28:01