filmov

tv

Testability of VLSI Lecture 4: Logic Simulation

Показать описание

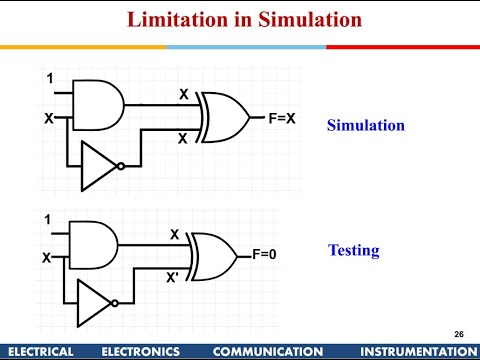

Simulation for Design Verification, True Value Simulation, Logic verification of a 32-bit ripple-carry adder, Fault simulation for test generation, Modeling Circuits for Simulation, Function or 1. Behavior Level, 2. Logic Level, 3. Switch Level, 4. Circuit Level, 5. Timing Level. Why Circuit Level Modeling Is Important, Modeling Gates for Z and X inputs, Modeling XOR/NOR Gate, Limitation in Simulation, Design for Testing, Modeling Circuits for Simulation, 1. Zero Delay Model, 2. Unit Delay Model, 3. Multiple Delay Model

Tr and Tf different for each type of gate. 4. Min. Max Delay, Algorithms for True-Value Simulation, Circuit Simplification, Circuit Levelization, Compiled-code simulations, Event-driven Simulation, Zero delay, Nominal delay.

Tr and Tf different for each type of gate. 4. Min. Max Delay, Algorithms for True-Value Simulation, Circuit Simplification, Circuit Levelization, Compiled-code simulations, Event-driven Simulation, Zero delay, Nominal delay.

1:29:53

1:29:53

0:51:50

0:51:50

0:26:05

0:26:05

0:14:56

0:14:56

0:56:04

0:56:04

0:30:01

0:30:01

1:30:42

1:30:42

1:24:16

1:24:16

1:40:19

1:40:19

1:18:28

1:18:28

1:34:17

1:34:17

1:09:24

1:09:24

1:48:41

1:48:41

0:57:27

0:57:27

0:26:12

0:26:12

1:25:53

1:25:53

1:02:35

1:02:35

0:06:57

0:06:57

0:00:18

0:00:18

0:24:11

0:24:11

0:00:37

0:00:37

0:00:15

0:00:15

0:30:47

0:30:47

0:53:43

0:53:43