filmov

tv

Behavioral Modeling Style Intro #ModelSim #Verilog

Показать описание

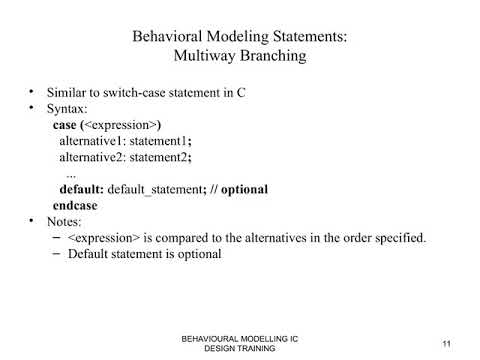

Behavioural modelling is the highest of level abstraction that completely depends on the circuit behaviour or on the truth table.

If you know how your circuit will behave, you can design it. In fact, you can design the module without knowing the components of the hardware.

However, even though it is the closest in terms of natural language understanding of the circuit functionality, this modelling type is hardest to implement and synthesize. Hence, it is utilized for complex circuits such as pure combinational or sequential circuits.

A module developed using behavioural modelling contains initial or always statements, which are executed concurrently (according to the parallelism of the model). The procedural statements in the module are executed sequentially.

At time=0, both the initial and always will execute and then, always statements run for the remaining time. Here’s the syntax:

always [timing control] procedural_statements;

initial [ timing control] procedural_statements;

If you know how your circuit will behave, you can design it. In fact, you can design the module without knowing the components of the hardware.

However, even though it is the closest in terms of natural language understanding of the circuit functionality, this modelling type is hardest to implement and synthesize. Hence, it is utilized for complex circuits such as pure combinational or sequential circuits.

A module developed using behavioural modelling contains initial or always statements, which are executed concurrently (according to the parallelism of the model). The procedural statements in the module are executed sequentially.

At time=0, both the initial and always will execute and then, always statements run for the remaining time. Here’s the syntax:

always [timing control] procedural_statements;

initial [ timing control] procedural_statements;

0:12:26

0:12:26

0:00:50

0:00:50

0:08:41

0:08:41

0:22:49

0:22:49

0:04:40

0:04:40

0:04:35

0:04:35

0:15:06

0:15:06

0:14:16

0:14:16

0:02:00

0:02:00

0:10:46

0:10:46

0:17:04

0:17:04

0:07:32

0:07:32

0:16:46

0:16:46

0:21:11

0:21:11

0:02:50

0:02:50

0:05:41

0:05:41

0:26:34

0:26:34

0:38:57

0:38:57

0:04:25

0:04:25

0:14:04

0:14:04

0:01:19

0:01:19

0:11:04

0:11:04

0:32:40

0:32:40