filmov

tv

OCR A-Level Computer Science: CPU Performance in 5 Minutes - H446 Revision

Показать описание

The Fetch-Decode-Execute Cycle is a cornerstone in understanding how CPUs process instructions. In this 5-minute breakdown tailored for OCR A-Level Computer Science students, we'll demystify the FDE Cycle, ensuring you're well-prepared for the H446 exam. Be sure to subscribe for more pinpointed 5-minute topic summaries!

2. OCR GCSE (J277) 1.1 CPU components and their function

3. OCR A Level (H406-H466) SLR1 - 1.1 Performance of the CPU

1. OCR A Level (H046-H446) SLR1 - 1.1 ALU, CU, registers and buses

OCR A-Level Computer Science: Types of Processor Explained in 5 Minutes - H446 Revision

4. OCR A Level (H466) SLR1 - 1.1 Pipelining

A-Level Computer Science - CPU Components in 5 minutes - OCR H446

1. OCR GCSE (J277) 1.1 The purpose of the CPU - The fetch-execute cycle

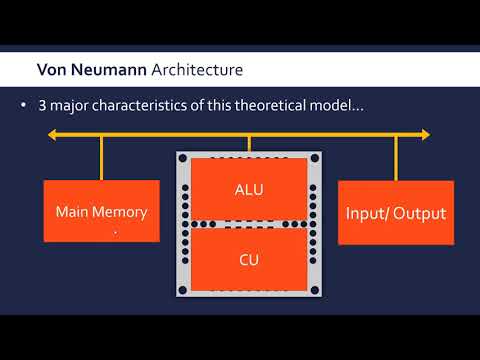

5. OCR A Level (H046-H466) SLR1 - 1.1 Von Neumann and Harvard

2. OCR A Level (H406-H466) SLR1 - 1.1 Fetch, decode, execute cycle

1.1.1 Common CPU Components - Revise GCSE Computer Science

7. OCR A Level (H446) SLR2 - 1.1 GPUs and their uses

6. OCR A Level (H046-H446) SLR2 - 1.1 CISC vs RISC

The CPU and Von Neumann Architecture

OCR A-Level Computer Science: CPU Performance in 5 Minutes - H446 Revision

8. OCR A Level (H046-H446) SLR2 - 1.1 Multi-core & parallel systems

3. OCR GCSE (J277) 1.1 Von Neumann architecture

1.1 Systems Architecture full topic revision | OCR J277 9-1 Computer Science

[InClass] GCSE OCR - Architecture of the CPU - Registers

OCR GCSE Computer Science Paper 1 in 30 mins

AQA A'Level Performance of the CPU

1.1 The Purpose Of The CPU | OCR GCSE Computer Science

OCR GCSE Computer Science with Mr Goff: 01. Architecture of the CPU

The Fetch-Execute Cycle: What's Your Computer Actually Doing?

OCR A-Level Computer Science: Fetch-Decode-Execute (FDE) Cycle in 5 Minutes - H446 Revision

Комментарии

0:03:00

0:03:00

0:06:17

0:06:17

0:12:33

0:12:33

0:05:11

0:05:11

0:06:25

0:06:25

0:04:56

0:04:56

0:03:52

0:03:52

0:03:14

0:03:14

0:13:05

0:13:05

0:03:29

0:03:29

0:07:27

0:07:27

0:10:28

0:10:28

0:09:23

0:09:23

0:06:56

0:06:56

0:06:38

0:06:38

0:13:50

0:13:50

0:14:15

0:14:15

![[InClass] GCSE OCR](https://i.ytimg.com/vi/QygLtknmees/hqdefault.jpg) 0:35:51

0:35:51

0:30:00

0:30:00

0:03:40

0:03:40

0:02:12

0:02:12

0:04:48

0:04:48

0:09:04

0:09:04

0:04:43

0:04:43