filmov

tv

How to get BCD from Binary with verilog and the Double Dabble algorithm!

Показать описание

**NOTE: the final Verilog script in this video is intended for 4 digit conversion where the initial example is for 3 digit conversion.**

In this video we go through the algorithm to create BCD (Binary Coded Decimal) from Binary with the double dabble method. We then show a verilog example of how to code the Double Dabble algorithm! BCD is a very important number coding in order to drive things like 7 segment LED displays and more. This code will eventually be uploaded to an FPGA board to drive a set of 7 segment displays. The code can be downloaded from my GitHub link below. Please keep an eye out in the description for the upcoming videos that tie into this project! Have a great day and don't forget to #LoveWell!!

GitHub Code:

Binary to BCD Simulation video:

BCD to 7 segment decode:

In this video we go through the algorithm to create BCD (Binary Coded Decimal) from Binary with the double dabble method. We then show a verilog example of how to code the Double Dabble algorithm! BCD is a very important number coding in order to drive things like 7 segment LED displays and more. This code will eventually be uploaded to an FPGA board to drive a set of 7 segment displays. The code can be downloaded from my GitHub link below. Please keep an eye out in the description for the upcoming videos that tie into this project! Have a great day and don't forget to #LoveWell!!

GitHub Code:

Binary to BCD Simulation video:

BCD to 7 segment decode:

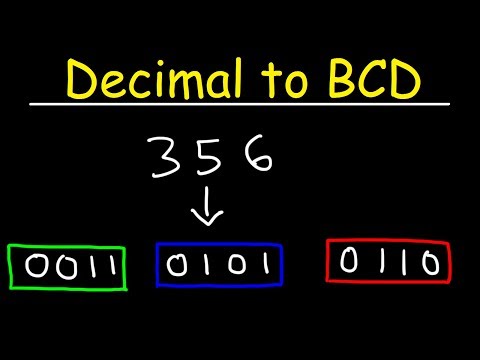

Decimal to BCD

How to get BCD from Binary with verilog and the Double Dabble algorithm!

BCD Codes (Binary Coded Decimal Codes) Explained

#8 Simple Demo of Binary Coded Decimal (BCD) for Real Time Clocks (such as the DS3231 and DS1307)

BCD Addition

Binary to Decimal conversion in scientific calculator

How To Convert Gray Code to Binary and Binary to Gray Code

Binary to BCD | Logical Redstone #10

BCD to binary conversion

How to get BCD on SimpleSwap without sign-up?

decimal to binary conversion #shorts #binary#trending #viral

Hexadecimal to decimal conversion in scientific calculator

How to inflate your bcd at the surface!

How To:Measure BRA Size #shorts_video #fashion #follow #bhfyp

The Secret to Perfect Buoyancy While Scuba Diving

decimal to binary conversion in Casio fx-991ES plus

Lec-8: BCD, Excess-3 Code & Conversion with example

How to Fix Windows 11 Won't Boot BCD Error Code 0xc0000098

Scuba Diving Skills: How to Inflate and Deflate your BCD Using the LPI | Scuba Equipment 101

How To Make Sure Your BCD Fits

ASCII Code and Binary

Scuba Diving: How to Assemble Equipment

Threading a BCD cam band is easy. See how it’s done #dive #scubadiving #divetips #bcd #shorts

Binary to Decimal Conversion

Комментарии

0:05:38

0:05:38

0:08:55

0:08:55

0:13:39

0:13:39

0:06:59

0:06:59

0:11:28

0:11:28

0:00:16

0:00:16

0:11:00

0:11:00

0:29:49

0:29:49

0:00:36

0:00:36

0:02:49

0:02:49

0:00:13

0:00:13

0:00:11

0:00:11

0:00:27

0:00:27

0:00:25

0:00:25

0:00:57

0:00:57

0:00:14

0:00:14

0:07:38

0:07:38

0:06:04

0:06:04

0:02:38

0:02:38

0:04:04

0:04:04

0:08:16

0:08:16

0:02:12

0:02:12

0:01:01

0:01:01

0:00:31

0:00:31