filmov

tv

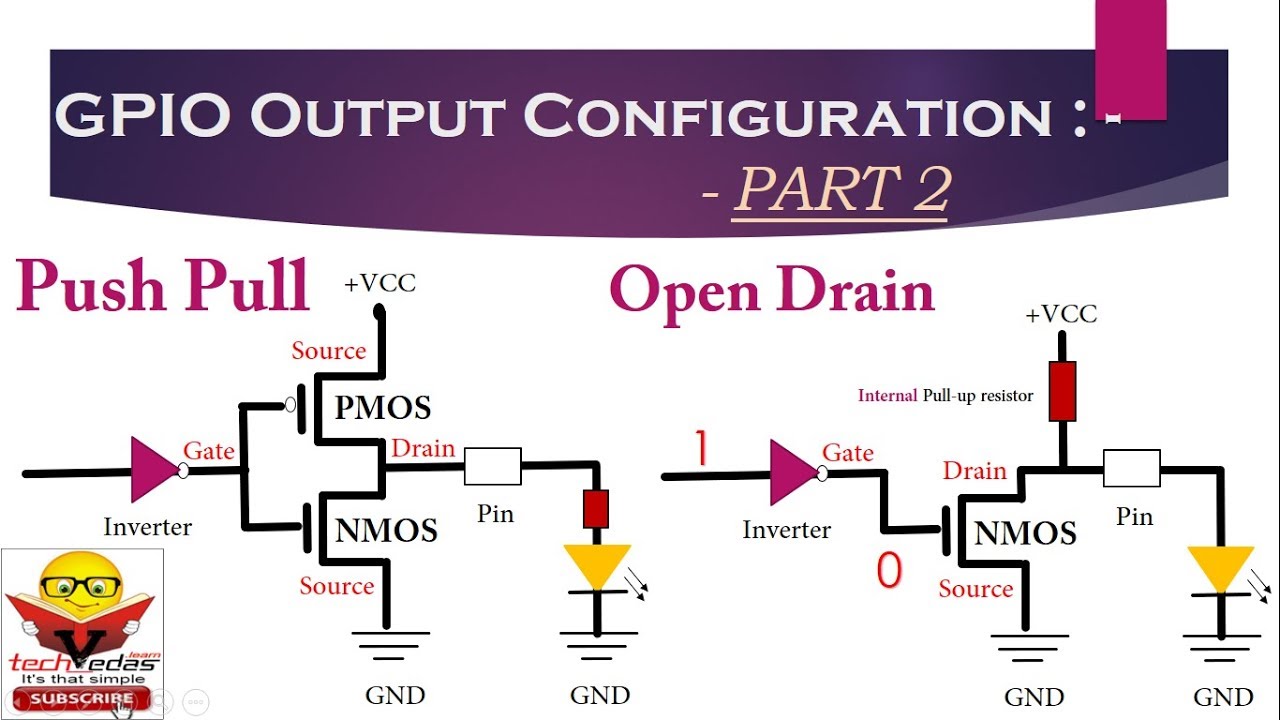

GPIO Output Configuration | Open Drain configuration | Push Pull configuration

Показать описание

Fundamentals29 GPIO Output Configuration or Open Drain configuration or Push-Pull configuration

Friends welcome to this video series on Embedded System. GPIO which stands for general purpose input output is one of the first things to play with while learning Embedded System programming.

So in this video, let's continue our discussion on this topic and try to understand what is the need of Pullup and pull down registers while making use of GPIOand some of the most commonly used GPIO output configurations like Push pull and Open Drain.

#TechVedasLearn

#GPIO

#GpioModes

#GeneralPurposeInputOutput

#GpioOutputConfiguraion

#OpenDrainConfiguraion

#PushPullConfiguraion

#HowToTurnOnLed

#PullUpResistor

#PullDownResistor

Video tutorial playlist link

Unified modeling language

Pointers in C

Embedded System

Friends welcome to this video series on Embedded System. GPIO which stands for general purpose input output is one of the first things to play with while learning Embedded System programming.

So in this video, let's continue our discussion on this topic and try to understand what is the need of Pullup and pull down registers while making use of GPIOand some of the most commonly used GPIO output configurations like Push pull and Open Drain.

#TechVedasLearn

#GPIO

#GpioModes

#GeneralPurposeInputOutput

#GpioOutputConfiguraion

#OpenDrainConfiguraion

#PushPullConfiguraion

#HowToTurnOnLed

#PullUpResistor

#PullDownResistor

Video tutorial playlist link

Unified modeling language

Pointers in C

Embedded System

GPIO Output Configuration | Open Drain configuration | Push Pull configuration

GPIO Output Mode: Working of Open Drain Configuration

Lecture 6: GPIO Output: Lighting up a LED

How GPIO works | General Purpose Input Output | GPIO Behind The Scene

The GPIO Configuration Parameters | STM GPIO | HAL

14 GPIO Must know concepts 005 GPIO output mode with open drain state

25 The logic of Push pull and Open drain modes in GPIO Output configuration

14 GPIO Must know concepts 006 GPIO output mode with push pull state

15 GPIO Programming structure and Registers 006 Output Configuration of a GPIO Pin in open drain m

GPIO Ouput Mode with Open Drain state

How to Blink a LED | #5 STM32 GPIO output

GPIO Working Explained Inside a Microcontroller

GPIO Pull-up/Pull-down resistors explained

GPIO Push-Pull Configuration [Microcontroller Output Mode]

Commodore 64, Open-Drain GPIO | Read and write on a single wire at the same time

12 Peripheral IO, learning GPIO output with an LED

Tutorial 5: Peripheral 1 - General purpose Input Output (GPIO) Configuration in STM32

BeagleBone Black GPIO (Output) Pin Configuration

💡Microcontroller GPIO from scratch🚀

STM32CubeMX GPIO out open drain 2

Chap 15.6 006 Output Configuration of a GPIO Pin in open drain mode

Stm32 Gpio Output configuration Example | LED BLINK | stm32 Nucleo board | stm32l476rg

Linus Walleij - GPIO and Pin Control for Embedded Systems

STM32 Programming for Beginners | Introduction to GPIO Pins

Комментарии

0:05:11

0:05:11

0:06:04

0:06:04

0:11:01

0:11:01

0:05:52

0:05:52

0:04:50

0:04:50

0:05:54

0:05:54

0:21:54

0:21:54

0:02:48

0:02:48

0:04:58

0:04:58

0:05:54

0:05:54

0:24:41

0:24:41

0:12:17

0:12:17

0:04:55

0:04:55

0:01:41

0:01:41

0:00:47

0:00:47

0:07:12

0:07:12

0:08:28

0:08:28

0:05:48

0:05:48

0:00:27

0:00:27

0:00:16

0:00:16

0:04:59

0:04:59

0:13:38

0:13:38

0:41:08

0:41:08

0:23:39

0:23:39