filmov

tv

SystemVerilog-Style Constraints and Functional Coverage in Python

Показать описание

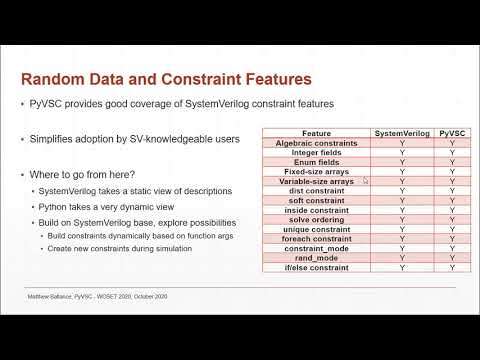

Matthew Ballance

While SystemVerilog is the most widely-used language for creating functional verification testbench environments, many different language are used as well. In the past decade or so, Python has risen in popularity as a verification language. The open-source Python ecosystem for functional verification provides many of the expected elements of any other functional verification flow, such as libraries for connecting Python to simulators, frameworks for structuring testbench environments, and bus functional models for specific protocols. However, until recently, the it did not provide support for specifying data-randomization constraints and functional coverage metrics in a way that SystemVerilog users would find familiar. This presentation will introduce PyVSC, an open-source Python library for modeling SystemVerilog-style data randomization constraints and functional coverage metrics in Python. It will describe the constraint and coverage features that can be modeled with PyVSC, and describe how PyVSC leverages existing SMT solvers to generate random data from complex sets of constraints. It will describe how functional coverage data collected by PyVSC can be exported to support manipulation by external flows and toolchains.

OpenHardware

The FOSSi Foundation is proud to announce Latch-Up, a conference dedicated to free and open source silicon.

Latch-Up: a weekend of presentations and networking for the open source silicon community, much like its European sister conference ORConf.

OpenHardware

Sun Apr 2 09:30:00 2023 at UCSB Henley Hall room 1010

While SystemVerilog is the most widely-used language for creating functional verification testbench environments, many different language are used as well. In the past decade or so, Python has risen in popularity as a verification language. The open-source Python ecosystem for functional verification provides many of the expected elements of any other functional verification flow, such as libraries for connecting Python to simulators, frameworks for structuring testbench environments, and bus functional models for specific protocols. However, until recently, the it did not provide support for specifying data-randomization constraints and functional coverage metrics in a way that SystemVerilog users would find familiar. This presentation will introduce PyVSC, an open-source Python library for modeling SystemVerilog-style data randomization constraints and functional coverage metrics in Python. It will describe the constraint and coverage features that can be modeled with PyVSC, and describe how PyVSC leverages existing SMT solvers to generate random data from complex sets of constraints. It will describe how functional coverage data collected by PyVSC can be exported to support manipulation by external flows and toolchains.

OpenHardware

The FOSSi Foundation is proud to announce Latch-Up, a conference dedicated to free and open source silicon.

Latch-Up: a weekend of presentations and networking for the open source silicon community, much like its European sister conference ORConf.

OpenHardware

Sun Apr 2 09:30:00 2023 at UCSB Henley Hall room 1010

0:34:40

0:34:40

0:24:52

0:24:52

0:18:07

0:18:07

0:05:42

0:05:42

![[08/10] Writing OOP-style](https://i.ytimg.com/vi/kPhSmZTv85Q/hqdefault.jpg) 0:10:19

0:10:19

0:03:30

0:03:30

0:06:55

0:06:55

0:48:07

0:48:07

![[01/10] Writing OOP-style](https://i.ytimg.com/vi/9LfTYCLbj9M/hqdefault.jpg) 0:16:23

0:16:23

![[09-10/10] Writing OOP-style](https://i.ytimg.com/vi/Fn07XJXTx3g/hqdefault.jpg) 0:14:55

0:14:55

![[02/10] Writing OOP-style](https://i.ytimg.com/vi/E8Lfcc-uCCU/hqdefault.jpg) 0:12:27

0:12:27

0:03:46

0:03:46

0:14:53

0:14:53

0:09:32

0:09:32

0:30:22

0:30:22

0:58:59

0:58:59

0:09:14

0:09:14

0:32:49

0:32:49

0:00:21

0:00:21

0:17:48

0:17:48

0:15:42

0:15:42

0:00:37

0:00:37

0:18:23

0:18:23

0:16:05

0:16:05