filmov

tv

AI’s Hardware Problem

Показать описание

Links:

AI acceleration is a software problem | George Hotz and Lex Fridman

AI’s Single Point of Failure | Rob Toews | TED

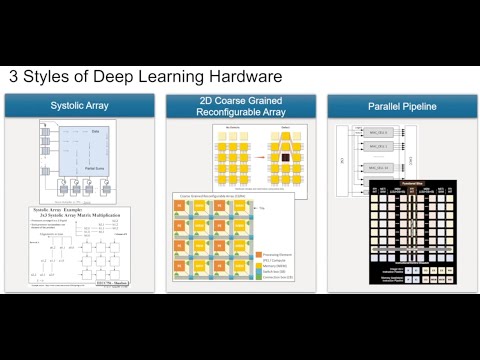

AI Hardware, Explained.

A Systematic Approach To Designing AI Accelerator Hardware

'AI' Has A Huge Problem

How AI is Killing Smartphones

The Coming AI Chip Boom

Steve Wozniak Reacts to Apple's New AI Tools

SM2322 Portable SSD Controller: Suited for Next-Generation AI Smart Devices and Gaming Consoles

I Had AI Troubleshoot Gaming PCs... Here's What Happened

Google TPU & other in-house AI Chips

Microsoft's AI-Powered CoPilot+ PCs Are Spyware

How AI Learned to Feel | 75 Years of Reinforcement Learning

This new AI is powerful and uncensored… Let’s run it

New Chinese AI Chips and their Huge Problems

Different Types Of AI Hardware

AI Hype: “Billions of dollars will be incinerated” Business Analysts Warn

How much does an AI ENGINEER make?

How much energy AI really needs. And why that's not its main problem.

Why hasn't Apple invented this yet?!

A.I. Expert Answers A.I. Questions From Twitter | Tech Support | WIRED

AI vs Machine Learning

All The Jobs AI Will Replace In 5 Years (And Jobs That It Won’t)

AI says why it will kill us all. Experts agree.

Комментарии

0:02:07

0:02:07

0:11:34

0:11:34

0:15:24

0:15:24

0:10:49

0:10:49

0:14:05

0:14:05

0:09:44

0:09:44

0:15:41

0:15:41

0:04:47

0:04:47

0:02:41

0:02:41

0:22:12

0:22:12

0:12:06

0:12:06

0:08:49

0:08:49

0:25:03

0:25:03

0:04:37

0:04:37

0:14:13

0:14:13

0:10:44

0:10:44

0:06:53

0:06:53

0:00:36

0:00:36

0:08:06

0:08:06

0:01:00

0:01:00

0:16:32

0:16:32

0:05:49

0:05:49

0:13:39

0:13:39

0:18:55

0:18:55