filmov

tv

Load Data from Files into Verilog and Vivado Simulations – FPGA Tutorial

Показать описание

#fpga #xilinx #vivado #amd #embeddedsystems #controlengineering #controltheory #verilog #hardware #hardwareprogramming #automation #digitallogic #digitallogicdesign #hardwaredescriptivelanguage #hdl #signalprocessing #dsp #digitalsignalprocessing #aleksandarhaber

It takes a significant amount of time and energy to create these free video tutorials. You can support my efforts in this way:

- You Can also press the Thanks YouTube Dollar button

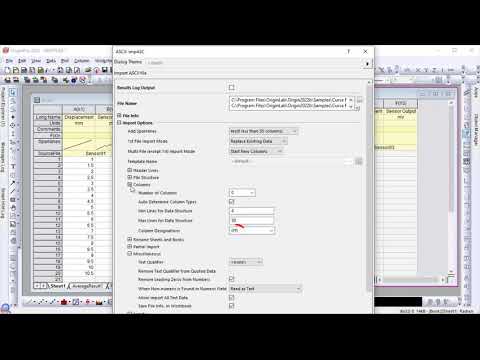

- In this FPGA, Verilog, and Vivado tutorial, we explain how to load data from files into a Verilog and Vivado simulation.

Motivation: The standard practice when developing and implementing FPGA algorithms is to first implement and test algorithms in MATLAB and Python. Some people use also use C/C++ programming languages for this purpose. This is done since it is significantly easier to test algorithms in MATLAB or Python than in FPGAs. After MATLAB or Python simulations convince us that algorithms work as expected, the next stage is to implement them in Verilog and to simulate them in the Vivado development environment. The final stage is the FPGA implementation. During testing and simulation in Verilog and Vivado, it is often necessary to load a test data sequence that is identical to the test data sequence which is used for algorithm simulation in Python and MATLAB. Consequently, we need to know how to load data from the external files into a Verilog simulation.

The material presented in this tutorial is very important for simulating algorithms implemented in Verilog.

It takes a significant amount of time and energy to create these free video tutorials. You can support my efforts in this way:

- You Can also press the Thanks YouTube Dollar button

- In this FPGA, Verilog, and Vivado tutorial, we explain how to load data from files into a Verilog and Vivado simulation.

Motivation: The standard practice when developing and implementing FPGA algorithms is to first implement and test algorithms in MATLAB and Python. Some people use also use C/C++ programming languages for this purpose. This is done since it is significantly easier to test algorithms in MATLAB or Python than in FPGAs. After MATLAB or Python simulations convince us that algorithms work as expected, the next stage is to implement them in Verilog and to simulate them in the Vivado development environment. The final stage is the FPGA implementation. During testing and simulation in Verilog and Vivado, it is often necessary to load a test data sequence that is identical to the test data sequence which is used for algorithm simulation in Python and MATLAB. Consequently, we need to know how to load data from the external files into a Verilog simulation.

The material presented in this tutorial is very important for simulating algorithms implemented in Verilog.

Комментарии

0:10:29

0:10:29

0:00:25

0:00:25

0:10:18

0:10:18

0:02:55

0:02:55

0:00:09

0:00:09

0:17:10

0:17:10

0:04:12

0:04:12

0:00:22

0:00:22

0:02:52

0:02:52

0:08:41

0:08:41

0:07:18

0:07:18

0:00:48

0:00:48

0:08:43

0:08:43

0:08:49

0:08:49

0:00:30

0:00:30

0:00:44

0:00:44

0:00:56

0:00:56

0:00:38

0:00:38

0:00:21

0:00:21

0:00:16

0:00:16

0:00:20

0:00:20

0:00:26

0:00:26

0:00:16

0:00:16

0:01:00

0:01:00