filmov

tv

Q9. b Multiplier and Accumulator (MAC) | DSP | EnggClasses

Показать описание

Multiplier and Accumulator (MAC), a special Digital Signal Processor hardware unit is been considered and explained in brief.

The video lecture covers:

1) The special hardware units.

2) Digital Signal Processors

3) Harvard Architecture

4) Von-Neuman Architecture

5) MAC

6) X- Register and Y- Register

7) Result Register

Course: Digital Signal Processing (DSP)

The video lecture covers:

1) The special hardware units.

2) Digital Signal Processors

3) Harvard Architecture

4) Von-Neuman Architecture

5) MAC

6) X- Register and Y- Register

7) Result Register

Course: Digital Signal Processing (DSP)

Q9. b Multiplier and Accumulator (MAC) | DSP | EnggClasses

Multiplier Accumulator Unit

DSP#68 Digital Signal Processor Hardware Unit || EC Academy

A Novel Architecture For Multiplier And Accumulator Unit By Using Parallel Prefix Adders | VLSI

Our Technology | Optical Multiply Accumulate (oMAC)

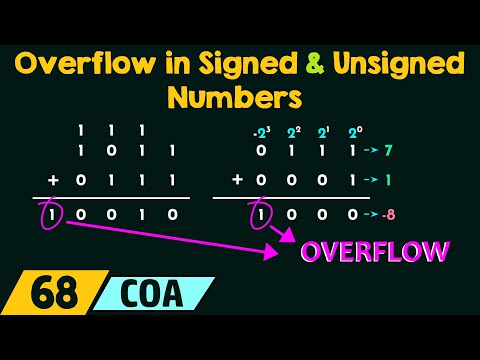

Overflow in Signed and Unsigned Numbers

19. Example on Accumulator CPU in CO

Multiplication Using Add Shift Method

Multiply and accumulate(MAC) Unit

FSM Accumulator in VHDL

Aspirants practicing eatingetiquette # SSB #SSBPreparation #NDA #CDS #Defence #DefenceAcademy

DSP Module 5 Hardware Units

When and how to use the Multiplier IP core

32 bit MAC unit design using vedic multiplier

An Efficient Design of 16 Bit MAC Unit using Vedic Mathematics

Performance Analysis of MAC Unit using Booth, Wallace Tree, Array and Vedic multipliers

Booth's Algorithm With Example | booths | booths algo

Efficient High Speed Computing Low Power Multiplier Architecture using Vedic Mathematics For....

FPGA Implementation of Booth Multiplier using Spartan6 FPGA project Board (9886387806)

Implementation of MAC by using Modified Vedic Multiplier 8-Bit

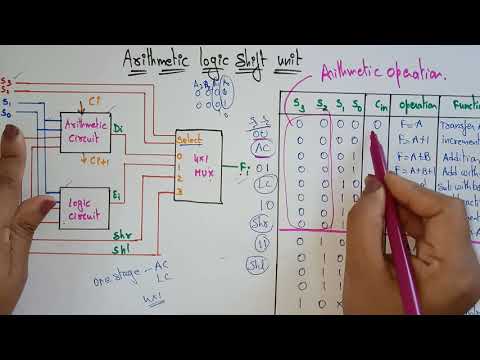

Arithmetic logic shift unit | Hardware implementation | COA

Example: Is an accumulator invertible?

8-bit Accumulator - Verilog Development Tutorial p.10

Q9.a Harvard Architecture for Digital Signal Processors | EnggClasses

Комментарии

0:02:07

0:02:07

0:04:51

0:04:51

0:06:59

0:06:59

0:02:18

0:02:18

0:00:37

0:00:37

0:10:11

0:10:11

0:10:31

0:10:31

0:11:00

0:11:00

0:53:19

0:53:19

0:01:33

0:01:33

0:00:11

0:00:11

0:16:50

0:16:50

0:05:45

0:05:45

0:15:46

0:15:46

0:07:17

0:07:17

0:17:43

0:17:43

0:07:29

0:07:29

0:18:59

0:18:59

0:00:20

0:00:20

0:03:34

0:03:34

0:13:28

0:13:28

0:02:24

0:02:24

0:19:24

0:19:24

0:05:10

0:05:10